32-Bit High-Performance Superscalar Processor Data Sheet

80960HA/HD/HT

74 Datasheet

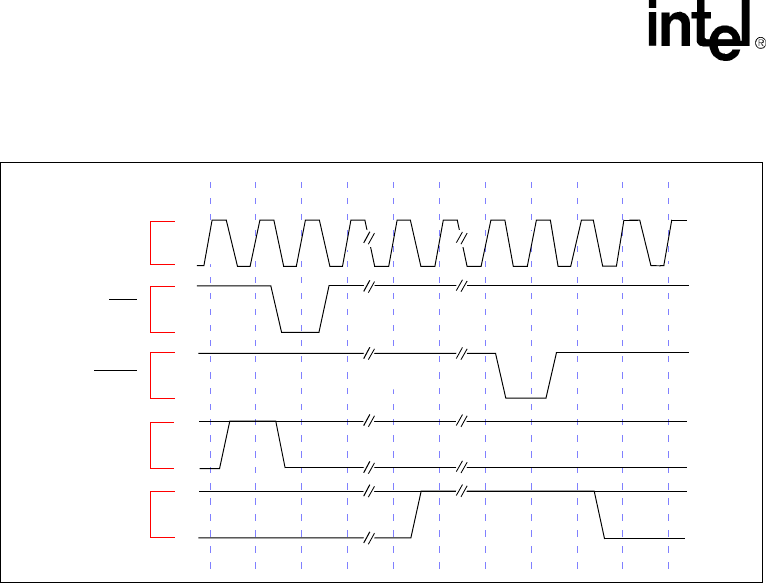

The processor may stall (BSTALL asserted) even with an empty bus queue (BREQ deasserted).

Depending on the instruction stream and memory wait states, the two signals may be separated by

several CLKIN cycles.

Bus arbitration logic that logically ‘ANDs’ BSTALL and BREQ will not correctly grant the bus to

the processor in all stall cases, potentially degrading processor performance.

Do not logically ‘AND’ BSTALL and BREQ together in arbitration logic. Instead, the simplest bus

arbitration should logically “OR” BSTALL and BREQ to determine the processor’s bus ownership

requirements.

More sophisticated arbitration should recognize the priority nature of these two signals. Using a

traffic light analogy, BREQ is a ‘yellow light’ warning of a possible processor stall and BSTALL is

a ‘red light’ indicating a stall in progress.

Figure 49. BREQ and BSTALL Operation

CLKIN

ADS

BLAST

BREQ

BSTALL