32-Bit High-Performance Superscalar Processor Data Sheet

80960HA/HD/HT

Datasheet 73

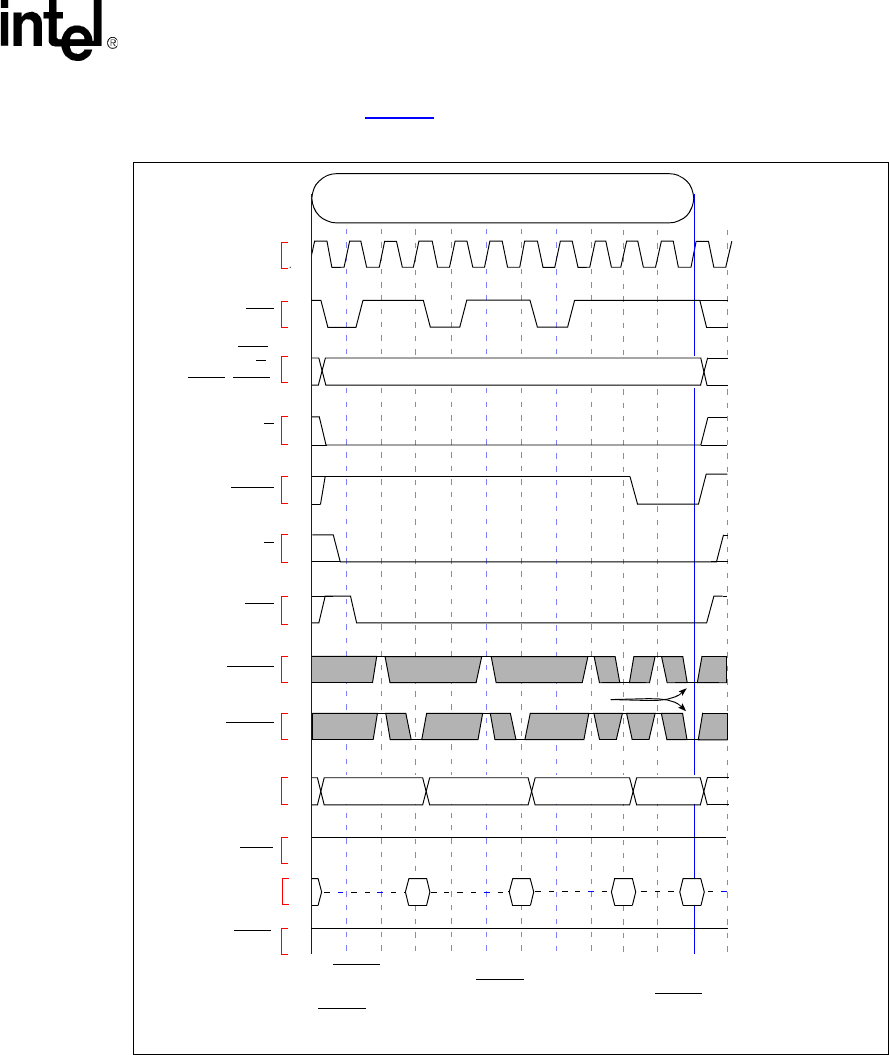

Figure 48. Terminating a Burst with BTERM

CLKIN

ADS

A31:4, SUP,

DT/R

DEN

READY

W/R

CT3:0, D/C,

BLAST

BTERM

A3:2

WAIT

D31:0,

BE3:0, LOCK

D0

D1 D2 D3

Valid

Quad-Word Read Request

N

RAD

= 0, N

RDD

= 0, N

RDA

= 0

Ready Enabled

00 01 10 11

Note: READY adds memory access time to data transfers, whether or not the

bus access is a burst access. BTERM

interrupts a bus access, whether or not

the bus access has more data transfers pending. Either the READY signal or

the BTERM signal terminates a bus access when the signal is asserted during

the last (or only) data transfer of the bus access.

See Note

DP3:0

PCHK

D1 AD1 DAA1D1