32-Bit High-Performance Superscalar Processor Data Sheet

80960HA/HD/HT

Datasheet 59

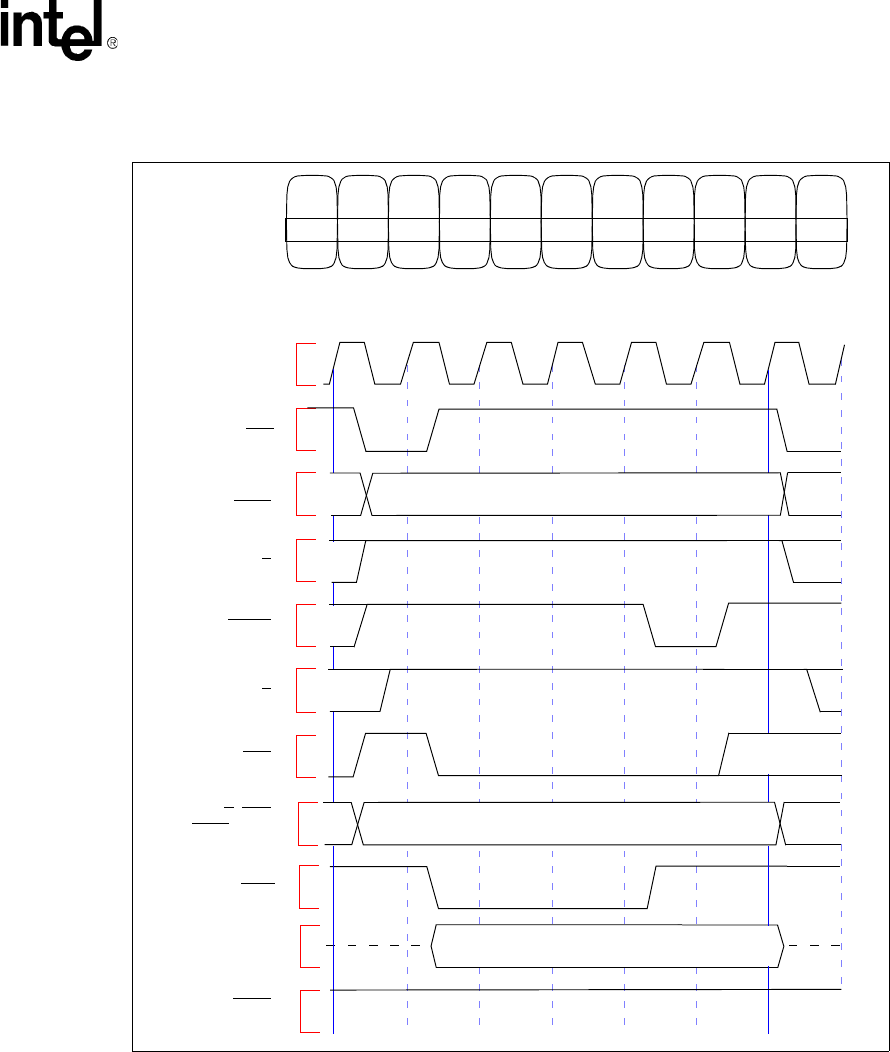

Figure 34. Non-Burst, Non-Pipelined Write Request with Wait States

ADS

A31:2,

W/R

BLAST

DT/R

DEN

WAIT

D31:0,

CLKIN

A3 21 D1

Out

A

Valid

Valid

BE3:0

DP3:0

PCHK

Burst

Bus

Width

Odd

Parity

N

XDA

N

WDD

N

WAD

N

RDD

29

28 2124 23-22 20 12-819-16 15-14 7-6 4-0

Disabled

0

OFF

0

1

0001

X

xx

X

x

Enabled

1

X

xxxxx

3

00011

X

xx

Disabled

0

X

xxxxx

Function

Bit

Value

External

Ready

Control

Pipe-

Lining Parity Enable

N

RAD

NOTE: Bits 31-30, 27-25, 13, and 5 are reserved.

PMCON

D/C, SUP,

LOCK, CT3:0