32-Bit High-Performance Superscalar Processor Data Sheet

80960HA/HD/HT

56 Datasheet

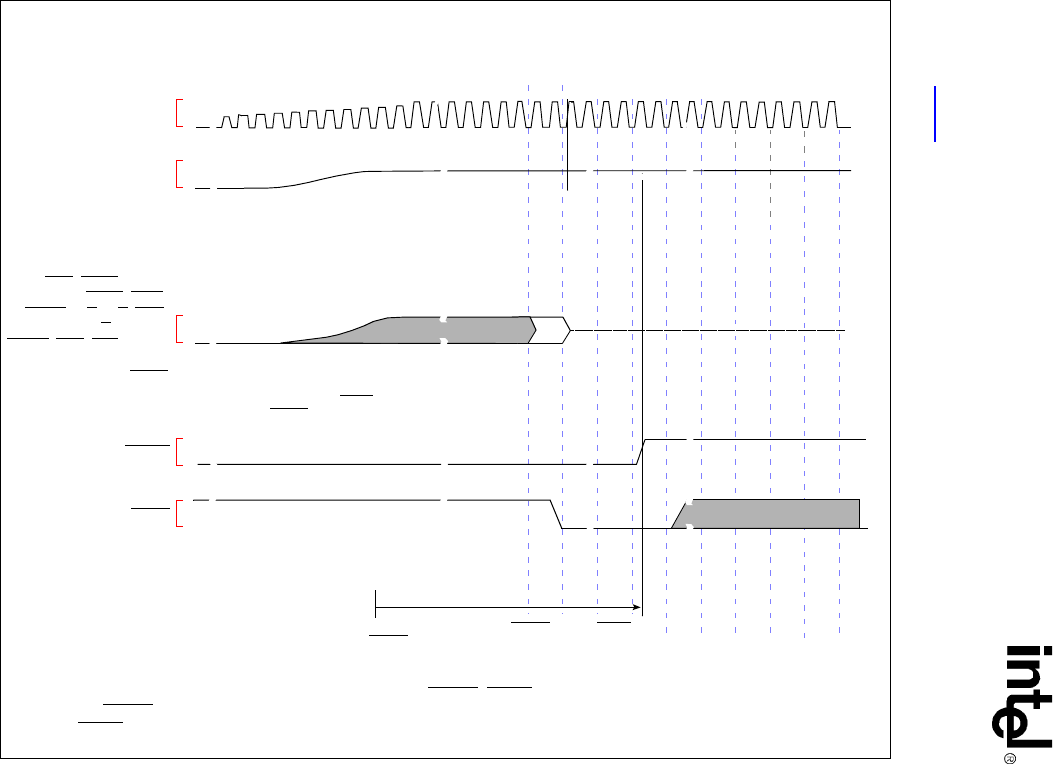

Figure 31. Entering ONCE Mode

CLKIN

ADS, BE3:0, A31:2,

RESET

ONCE

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

CLKIN and V

CC

Stable and RESET low and ONCE low to

RESET

high, minimum

10,000 CLKIN Periods.

D31:0, LOCK

, WAIT,

BLAST

,W/R, D/C, DEN,

DT/R

, HOLDA,

CT3:0, BSTALL, DP3:0,

PCHK

BLAST, FAIL, SUP,BREQ,

V

CC,

VCC5

∼

∼

∼

∼

∼

∼

∼

∼

ONCE mode is entered within 1 CLKIN

period after ONCE

becomes low while

RESET

is low.

∼

∼

∼

∼

∼

∼

∼

∼

CLKIN may neither float nor remain idle.

It must continue to run.

NOTES:

1. ONCE mode may be entered prior to the rising edge of RESET

: ONCE input is not latched until the rising

edge of RESET.

2. The ONCE input may be removed after the processor enters ONCE mode.