32-Bit High-Performance Superscalar Processor Data Sheet

80960HA/HD/HT

54 Datasheet

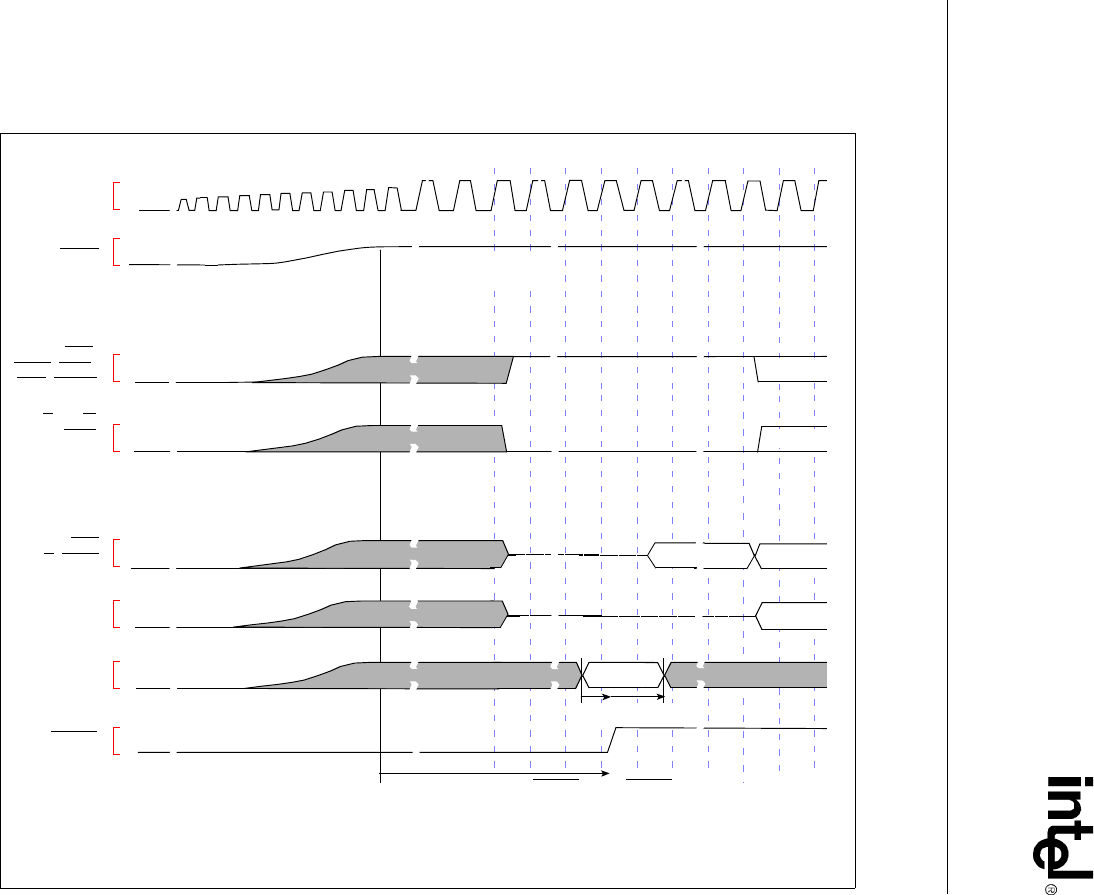

5.0 Bus Waveforms

Figure 29. Cold Reset Waveform

CLKIN

CT3:0, ADS

,

W/R

, DT/R,

D31:0,

STEST

RESET

V

CC,

VCC5,

LOCK, WAIT,

DEN

, BLAST

BREQ, FAIL,

DP3:0

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

Invalid

Valid

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

Inputs

Tsetup

1CLKIN

Thold

1CLKIN

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

∼

A31:2, SUP

D/C, BE3:0

BABA

~

~

∼

∼

∼

∼

ONCE

NOTE: V

CC

stable: As specified in Table 21, “VDIFF Specification for Dual Power Supply Requirements (3.3 V, 5 V)” on page 39

RESET high to First Bus Activity,

HA=67, HD=34, HT=23

CLKIN periods

CLKIN and V

CC

Stable to RESET high,

minimum 10,000 CLKIN periods

for PLL stabilization.

BSTALL