32-Bit High-Performance Superscalar Processor Data Sheet

80960HA/HD/HT

Datasheet 85

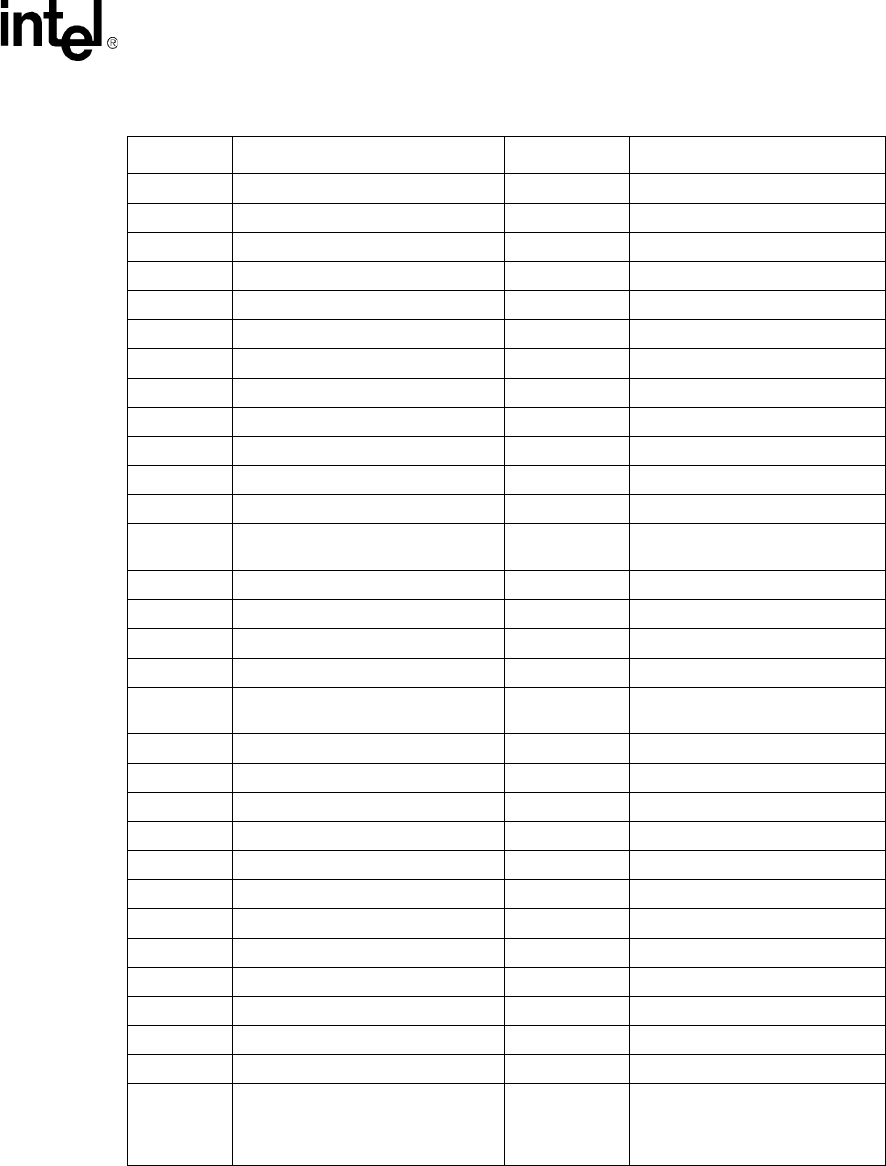

D21 Bidirectional

D22 Bidirectional

D23 Bidirectional

D24 Bidirectional

D25 Bidirectional

D26 Bidirectional

D27 Bidirectional

D28 Bidirectional

D29 Bidirectional

D30 Bidirectional

D31 Bidirectional

BTERMBAR Input

RDYBAR Input

Appears as READYBAR in BSDL

file.

HOLD Input

HOLDA Output

Enable for HOLDA control Control

ADSBAR Output

BE3BAR Output

Appears as BEBAR(3:0) in BSDL

file.

BE2BAR Output

BE1BAR Output

BE0BAR Output

BLASTBAR Output

DENBAR Output

WRRDBAR Output Appears as WRBAR in BSDL file.

DTRBAR Output

Enable for DTRBAR Control

WAITBAR Output

BSTALL Output

DATACODBAR Output Appears as DCBAR in BSDL file.

USERSUPBAR Output Appears as SUPBAR in BSDL file.

Enable for ADSBAR, BEBAR,

BLASTBAR, DENBAR, WRRDBAR,

WAITBAR, DCBAR, SUPBAR and

LOCKBAR,

Control

Table 26. 80960Hx Boundary Scan Chain (Sheet 2 of 4)

# Boundary Scan Cell Cell Type Comment

NOTES:

1. Cell#1 connects to TDO and cell #112 connects to TDI.

2. All outputs are tri-state.

3. In output and bidirectional signals, a logical 1 on the enable signal enables the output. A logical 0

tri-states the output.