32-Bit High-Performance Superscalar Processor Data Sheet

80960HA/HD/HT

Datasheet 83

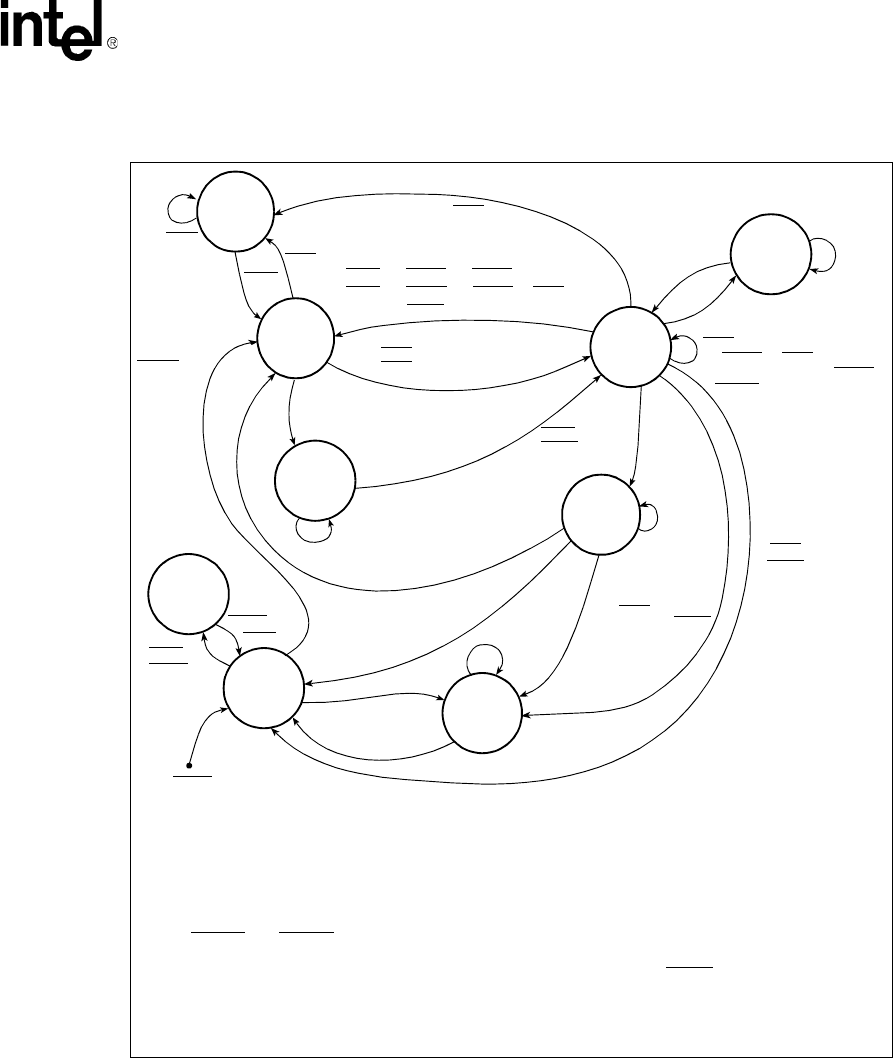

Figure 59. Bus States

Ti = IDLE

Th = HOLD

Ta = ADDRESS

Td = DATA

Tb = BOFF’ed

Taw= address to data wait

To = ONCE

Ta

Tb

Td

1

Taw

2

Trw

4

Tdw

3

Th

Ti

To

Tdw= data to data wait

Tdw= data to address wait

!BOFF and READ and N

rdd

= 0

READ and N

rdd

> 0 or

WRITE and N

wdd

> 0

BOFF

W

d

CNT = 1

!BOFF

and

W

a

CNT = 1

W

x

CNT=1 and

HOLD

W

x

CNT > 1

BOFF

!BOFF

HOLD

HOLD

!HOLD

NOTES:

1. When the PMCON for the region has External Ready Control enabled, wait states are inserted as long

as READY

and BTERM are de-asserted. When Read Pipelining is enabled, the Ta state of the

subsequent read access is concurrent with the last data cycle of the access. Because External Ready

Control is disabled for Read Pipelining, the address cycle occurs during BLAST

.

2. W

a

CNT is decremented during T

aw.

3. W

d

CNT is decremented during T

dw.

4. W

x

CNT is decremented during T

rw.

!HOLD and W

x

CNT=1

and !REQUEST

!HOLD and W

x

CNT=1

and REQUEST

!RESET

and

!HOLD and

REQUEST

RESET

and

ONCE

and

RESET

W

a

CNT > 1

READ and N

rad

> 0 or

WRITE and N

wad

> 0

!BOFF

and READ and N

rad

= 0 or

!BOFF

and WRITE and N

wad

= 0

!BOFF

and READY and !BLAST or

!HOLD and BLAST

and REQUEST and N

XDA

= 0

W

d

CNT > 1

KEY:

!BOFF and

and N

xda

= 0

HOLD and BLAST

!BOFF and !HOLD and

N

xda

= 0

BLAST

and

and !BLAST or !BOFF and

WRITE and N

wdd

= 0 and !BLAST

or

N

xda

> 0

REQUEST= One or more

requests in the bus queue.

READ= The current

access is a read.

WRITE= The current

access is a write.

RESET

BLAST and

BOFF

and !REQUEST

!ONCE

READY!

!BOFF and BTERM and !BLAST or !BOFF and