32-Bit High-Performance Superscalar Processor Data Sheet

80960HA/HD/HT

Datasheet 43

T

IS2

Input Setup for READY

, BTERM, HOLD, and

BOFF

6ns

T

IH2

Input Hold for READY

, BTERM, HOLD, and

BOFF

2.5 ns

Relative Output Timings

1, 2, 3, 6, 10

T

AVSH1

A31:2 Valid to ADS Rising T – 5T + 5ns10

T

AVSH2

BE3:0, W/R, SUP, D/C Valid to ADS Rising T – 5T + 5ns10

T

AVEL1

A31:2 Valid to DEN Falling T – 5T + 5ns10

T

AVEL2

BE3:0, W/R, SUP Valid to DEN Falling T – 5T + 5ns10

T

NLQV

WAIT Falling to Output Data Valid -5 5 ns 10

T

DVNH

Output Data Valid to WAIT Rising -5 + N*T 5 + N*T ns 4, 10

T

NLNH

WAIT Falling to WAIT Rising -4 + N*T 4 + N*T ns 4, 10

T

NHQX

Output Data Hold after WAIT Rising

-5 +

(N+1)*T

5 + (N+1)*T ns 5, 10

T

EHTV

DT/R Hold after DEN High T/2 – 5 Infinite ns 10

T

TVEL

DT/R

Valid to DEN Falling

80960HA

80960HD

80960HT

T/2 – 4

T/4 – 4

T/6 – 4

ns

ns

ns

10

Relative Input Timings

1, 7, 10

T

IS7

XINT7:0, NMI Input Setup 6 ns 9

T

IH7

XINT7:0, NMI Input Hold 2.5 ns 9

T

IS8

RESET Input Setup 3 ns 8

T

IH8

RESET Input Hold T/4 + 1 ns 8

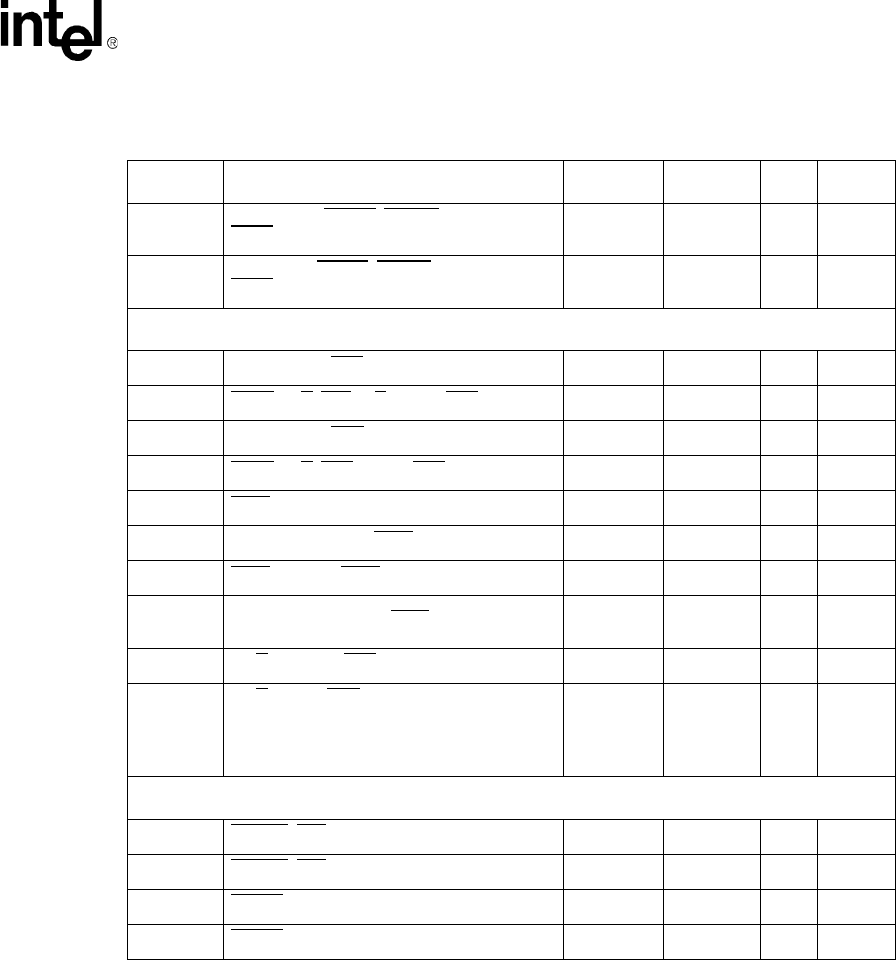

Table 23. 80960Hx A.C. Characteristics (Sheet 2 of 2)

Per conditions in Section 4.2, “Operating Conditions” on page 37 and Section 4.7.1, “AC Test Conditions” on page 45.

Symbol Parameter Min Max Units Notes

NOTE: See Table 24, “AC Characteristics Notes” on page 44 for all notes related to AC specifications.