64-bit Intel Xeon Processor MP with 1MB L2 Cache Specification Update

64-bit Intel

®

Xeon

®

Processor MP with up to 1 MB L2 Cache Specification Update 13

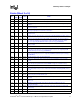

Summary Table of Changes

J49 X X No Fix Writes to IA32_MISC_ENABLE may not update flags for both logical processors

J50 X X No Fix Execute disable bit set with CR4.PAE may cause livelock

J51 X X No Fix Checking of page table base address may not match the address bit width supported by the

platform

J52 X X No Fix IA32_MCi_STATUS MSR may improperly indicate that additional MCA information may

have been captured

J53 X X No Fix With Trap Flag (TF) asserted, FP instruction that triggers an unmasked FP exception may

take single step trap before retirement of instruction

J54 X X No Fix PDE/PTE loads and continuous locked updates to the same cache line may cause a

system livelock

J55 X X No Fix Branch Trace Store (BTS) and Precise Event Based Sampling (PEBS) may update memory

outside the BTS/PEBS buffer

J56 X X No Fix L-bit of the CS and LMA bit of the IA32_EFER register may have an erroneous value for

one instruction following a mode transition in a Hyper-Threading Technology enabled

processor supporting Intel® Extended Memory 64 Technology (Intel® EM64T)

J57 X X No Fix Control Register 2 (CR2) can be updated during a REP MOVS/STOS instruction with fast

strings enabled

J58 X X No Fix REP STOS/MOVS instructions with RCX >= 2^32 may cause a system hang

J59 X X No Fix An REP MOVS or an REP STOS instruction with RCX >= 2^32 may fail to execute to

completion or may write to incorrect memory locations on processors supporting Intel®

Extended Memory 64 Technology (Intel® EM64T)

J60 X X No Fix An REP LODSB or an REP LODSD or an REP LODSQ instruction with RCX >= 2^32 may

cause a system hang on processors supporting Intel® Extended Memory 64 Technology

(Intel® EM64T)

J61 X X No Fix CPUID instruction returns incorrect brand string

J62 X X No Fix Data access which spans both canonical and non-canonical address space may hang

system

J63 X X No Fix Running in System Management Mode (SMM) and l1 data cache adaptive mode may

cause unexpected system behavior when SMRAM is mapped to cacheable memory

J64 X No Fix A#[39:36] always have On Die Termination (ODT) enabled

J65 X X No Fix A 64-bit value of Linear Instruction Pointer (LIP) may be reported incorrectly in the Branch

Trace Store (BTS) memory record or in the Precise Event Based Sampling (PEBS) memory

record

J66 X X Plan Fix It is possible that two specific invalid opcodes may cause unexpected memory accesses

J67 X X

No Fix

At Core-to-bus ratios of 16:1 and above Defer Reply transactions with non-zero REQb

values, may cause a Front Side Bus stall

J68 X X No Fix The processor may issue Front Side Bus transactions up to 6 clocks after RESET# is

asserted

J69 X X No Fix Front Side Bus machine checks may be reported as a result of on-going transactions during

warm reset

J70 X X No Fix Writing the Local Vector Table (LVT) when an interrupt is pending may cause an

unexpected interrupt

J71 X X No Fix The processor may issue multiple code fetches to the same cache line for systems with

slow memory

J72 X X No Fix IRET under certain conditions may cause an unexpected alignment check exception

J73 X X No Fix Using 2M/4M pages when A20M# is asserted may result in incorrect address translations.

Errata (Sheet 3 of 4)

No.

A-0/

0F41h

B-0/

0F49H

Plans Errata