Datasheet

C505/C505C/C505A/C505CA

Data Sheet 71 12.00

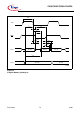

AC Characteristics (20 MHz, 0.5 Duty Cycle)

(Operating Conditions apply)

(

C

L

for port 0, ALE and PSEN outputs = 100 pF; C

L

for all other outputs = 80 pF)

Program Memory Characteristics

*)

Interfacing the C505 to devices with float times up to 20 ns is permissible. This limited bus contention will not

cause any damage to port 0 drivers.

Parameter Symbol Limit Values Unit

20 MHz clock

0.5 Duty Cycle

Variable Clock

1/CLP = 2 MHz to 20 MHz

min. max. min. max.

ALE pulse width

t

LHLL

35 – CLP - 15 – ns

Address setup to ALE

t

AVLL

10 – CLP/2 - 15 – ns

Address hold after ALE

t

LLAX

10 – CLP/2 - 15 – ns

ALE to valid instruction in

t

LLIV

– 55 – 2 CLP - 45 ns

ALE to PSEN

t

LLPL

10 – CLP/2 - 15 – ns

PSEN

pulse width t

PLPH

60 – 3/2 CLP

- 15

– ns

PSEN

to valid instruction in t

PLIV

– 25 – 3/2 CLP

- 50

ns

Input instruction hold after PSEN

t

PXIX

0 – 0 – ns

Input instruction float after PSEN

t

PXIZ

*)

– 20 – CLP/2 - 5 ns

Address valid after PSEN

t

PXAV

*)

20 – CLP/2 - 5 – ns

Address to valid instruction in

t

AVIV

– 65 – 5/2 CLP

- 60

ns

Address float to PSEN

t

AZPL

- 5 – - 5 – ns