Specifications

ESS Technology, Inc. SAM0023-122898 95

ES1869 DATA SHEET

APPENDIX C: I

2

S ZV INTERFACE REFERENCE

Audio Interface Timing

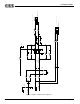

Figure 37 Audio Interface Timing

LRCLK

This signal determines which audio channel (left/right) is

currently being input on the audio Serial Data input line.

LRCLK is low to indicate the left channel and high to

indicate the right channel. Typical frequency values for this

signal are 48 kHz, 44.1 kHz, 32 kHz, and 22 kHz.

SCLK

This signal is the serial digital audio PCM clock.

SDATA

This signal is the digital PCM signal that carries audio

information. Digital audio data is transferred using I

2

S

format.

MCLK

This signal is the Master clock for the digital audio. MCLK

is asynchronous to LRCLK, SDATA, and SCLK.

The MCLK must be either 256x or 384x the desired Input

Word Rate (IWR). IWR is the frequency at which words for

each channel are input to the DAC and is equal to the

LRCLK frequency. The following table illustrates several

standard audio word rates and the required MCLK and

LRCLK frequencies. Typically, most devices operate with

384 Fs master clock.

The ZV Port audio DAC should support a MCLK frequency

of 384 Fs. This results in the frequencies shown below.

LRCLK

SCLK

SDATA

t

slrs

t

SCLKl

t

sdlrs

t

sdh

t

SCLKh

t

slrd

Table 31 AC Parameters for Audio Signals

Symbol Parameter Min

t

slrd

LRCLK delay 2 ns

t

slrs

LRCLK setup 32 ns

t

SCLKl

bit clock low 22 ns

t

SCLKh

bit clock high 22 ns

t

sdlrs

data setup 32 ns

t

sdh

data hold 2 ns

LRCLK (kHz)

Sample Frequency

SCLK (MHz)

32 x Fs

MCLK (MHz)

384x Fs

22 0.704 8.448

32 1.0240 12.2880

44.1 1.4112 16.9344

48 1.5360 18.4320