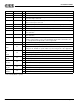

Specifications

8 SAM0023-122898 ESS Technology, Inc.

ES1869 DATA SHEET

PIN DESCRIPTION

XO 79 O Crystal oscillator output. Connect to external 14.318 MHz crystal.

RESET 81 I Active-high reset from the ISA bus.

FSR 82 I Input with internal pull-down. Frame sync for receive data from external DSP. Programma-

ble for active-high or active-low.

FSX 83 I Input with internal pull-down. Frame sync for transmit request from external DSP. Program-

mable for active-high or active-low.

DCLK 84 I Input with internal pull-down. Serial data clock from external DSP. Typically 2.048 MHz.

DR 85 I Input with internal pull-down. Data receive pin from external DSP.

DX 86 O Tri-state output. Data transmit to external DSP. High impedance when not transmitting.

MSD 87 I Input with internal pull-down. Music serial data from external ES689/ES69x wavetable

music synthesizer.

MCLK 88 I Input with internal pull-down. Music serial clock from external ES689/ES69x wavetable

music synthesizer.

SE 89 I Input with internal pull-down. Active-high to enable serial mode, that is, it enables an exter-

nal DSP to control analog resources of the ES1869 through the DSP serial interface. This

pin is logically OR’d internally with bit 7 of mixer register 48h.

RSTB 90 O Inverted RESET output.

GPDACK

91

O Active-low DMA acknowledge output to general-purpose device that uses DMA.

GPO1

O Output that is set high by external reset and thereafter controlled by bit 1 of port

Audio_Base+7h. Available to system software for power management or other applications.

GPDRQ

92

I DMA request output from general-purpose device based on the PnP configuration.

GPI I General-purpose input option.

GPIRQ I Interrupt request output from the general-purpose device based on the PnP configuration.

A15

1

93

I Address input from the ISA bus.

CDIRQ

0

I Interrupt request input from the IDE interface.

A14

1

94

I Address input from the ISA bus.

CDCSB0

0

O Active-low IDE interface chip select #0.

A13

1

95

I Address input from the ISA bus.

CDCSB1

0

O Active-low IDE interface chip select #1.

A12

1

96

I Address input from the ISA bus.

CDENBL

0

O Active-low IDE data bus transceiver enable.

0: Pins enabled by MODE = 0 (pin 60).

1: Pins enabled by MODE = 1 (pin 60).

Name Number I/O Description