User's Manual

Table Of Contents

- 1. Overview

- 2. Applications

- 3. Features

- 4. Technical data

- 5. Mechanical size

- 6. Soldering profile

- 7. Pin assignment

- 8. PCB design

- 9. Clock

- 10. Application circuits

- 11. Programming

- 12. Pre-flashed firmware

- 13. Adapter boards

- 14. Radio certification

- 15. Ordering information

- 16. Packaging dimension

- 17. Revision notes

- 18. References

User Manual

Version 1.1c

2013-07-01

OEM radio modules deRFmega

www.dresden-elektronik.de

Page 29 of 52

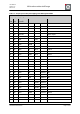

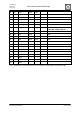

Table 7-5: I/O port pin to LGA pad mapping for deRFmega128-22M12

I/O port pin mapping

LGA

Pad

MCU

Pin

Primary

function

Alternate functions

Comments

1

-

GND

2

-

VCC

2.0 V to 3.6 V

3

11

TST

Must be connected to GND!

4

12

RSTN

Reset

5

13

RSTON

Reset output

6

14

PG0

DIG3

Internal connected to PA-CTX

4

7

15

PG1

DIG1

Internal connected to PA-ANTSEL

4

8

16

PG2

AMR

9

19

PG5

OC0B

10

53

PE7

ICP3

INT7

CLKO

11

52

PE6

T3

INT6

Timer3

12

28

PD3

TXD1

INT3

UART1

13

27

PD2

RXD1

INT2

UART1

14

33

CLKI

External clock input

15

32

PD7

T0

16

25

PD0

SCL

INT0

TWI

17

26

PD1

SDA

INT1

TWI

18

30

PD5

XCK1

19

31

PD6

T1

Internal connected to PA-CSD

4

20

36

PB0

SS

PCINT0

SPI

21

38

PB2

MOSI

PDI

PCINT2

SPI, ISP

22

37

PB1

SCK

PCINT1

SPI

23

39

PB3

MISO

PDO

PCINT3

SPI, ISP

24

40

PB4

OC2A

PCINT4

25

41

PB5

OC1A

PCINT5

26

42

PB6

OC1B

PCINT6

27

43

PB7

OC0A

OC1C

PCINT7

28

46

PE0

RXD0

PCINT8

UART0

29

47

PE1

TXD0

UART0

30

48

PE2

XCK0

AIN0

UART0

4

See Section 7.3.1