User manual

DLP-USB245M User Manual

Copyright © DLP Design 2002 Page 10 of 15

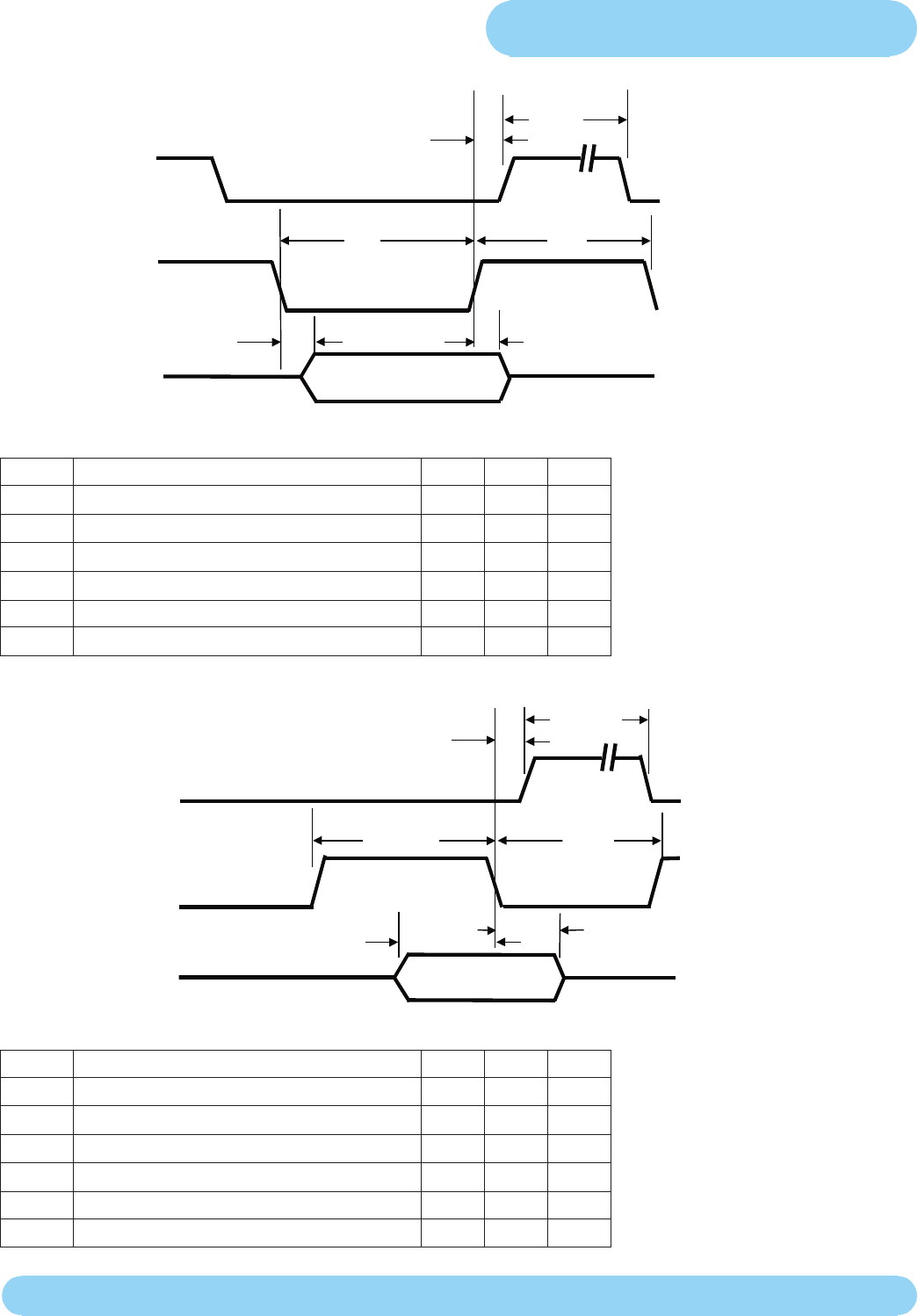

DLP-USB245M TIMING DIAGRAM – FIFO READ CYCLE

DLP-USB1 TIMING DIAGRAM – FIFO WRITE CYCLE

Time Description Min Max Unit

T1 RD Active Pulse Width 50 ns

T2 RD to RD Pre-Charge Time 50 ns

T3 RD Active to Valid Data 30 ns

T4 Valid Data Hold Time from RD Inactive 10 ns

T5 RD Inactive to RXF# 5 25 ns

T6 RXF inactive after RD cycle 80 ns

Time Description Min Max Unit

T7 WR Active Pulse Width 50 ns

T8 WR to WR Pre-Charge Time 50 ns

T9 Data Setup Time before WR inactive 20 ns

T10 Data Hold Time from WR inactive 10 ns

T11 WR Inactive to TXE# 5 25 ns

T12 TXE inactive after RD cycle 80 Ns

T6

T5

RXF#

T1 T2

RD#

T3 T4

D

Description Min Max Unit

Valid data

D[7..0]

Valid data

D[7..0]

T10

T9

TXE#

WR

T11

T12

T7

T8