Data Sheet

10/3/2018 JTAG-SMT3-NC Reference Manual [Reference.Digilentinc]

https://reference.digilentinc.com/reference/programmers/jtag-smt3/reference-manual 6/16

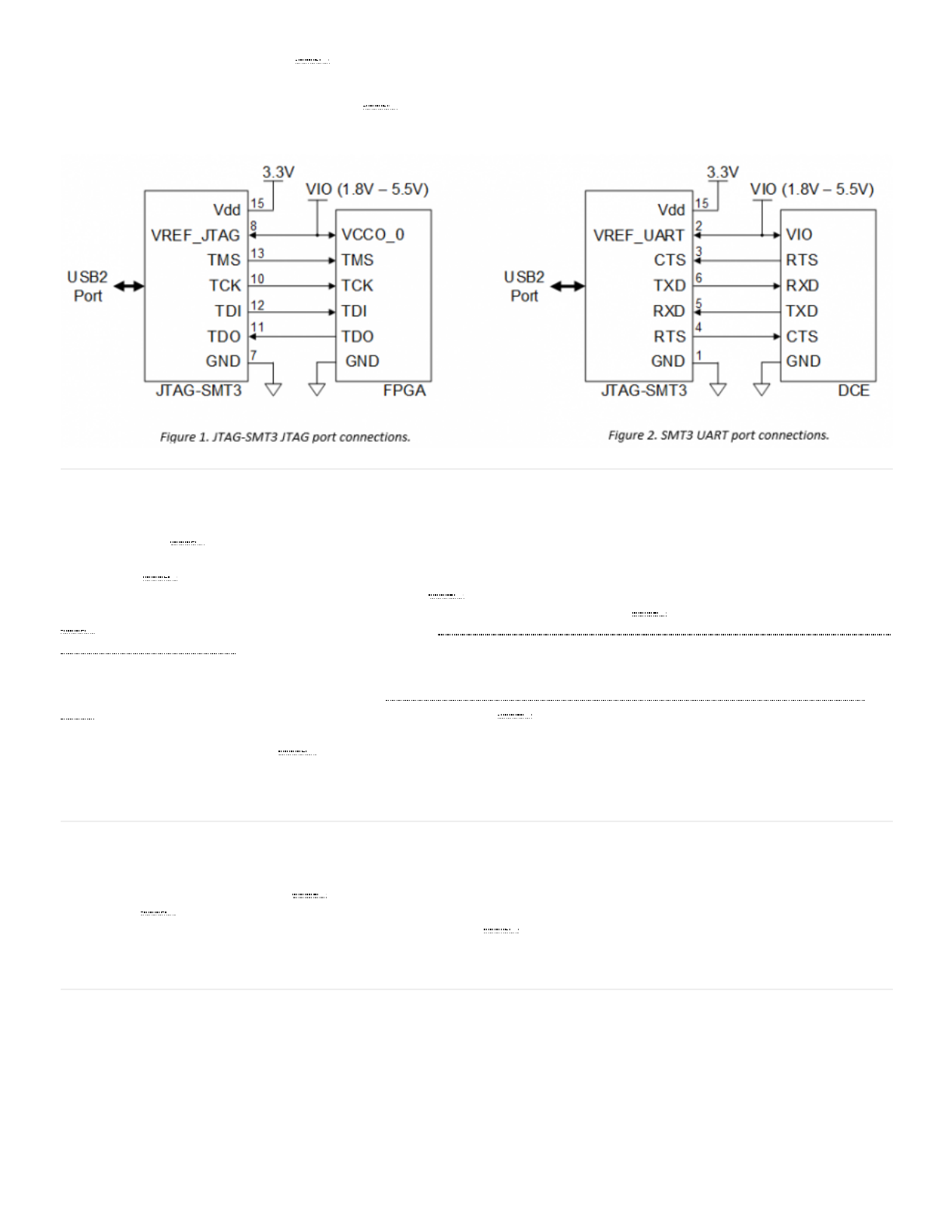

Note: Keep the impedance between the SMT3-NC () and FPGA below 100 Ohms to operate the JTAG at maximum speed. Note: If series resistors are used, they

should be placed near the transmitting end in order to minimize reflections.

In addition to supporting JTAG, the JTAG-SMT3-NC () also features a UART Interface that allows communication with UART peripherals

(see Fig. 2). The UART interface is presented as a virtual com port on the host PC, supports baud rates up to 12Mbaud, and has an

independent voltage reference which allows it to interface with devices operating at voltages between 1.8V and 5.5V.

The JTAG-SMT3-NC () has been designed to work seamlessly with Xilinx’s ISE® (iMPACT, ChipScope, EDK, and eFuse) and Vivado

tool suites. The most recent versions of ISE and Vivado include all of the drivers, libraries, and plugins necessary to communicate with the

JTAG-SMT3-NC (). At the time of writing, the following Xilinx software included support for the SMT3: Vivado 2017.1+, Vivado 2016.1+,

Vivado 2015.1+, Vivado 2014.1+, and ISE 14.1+. The SMT3-NC () is also compatible with ISE 13.1 - 13.4; however, these versions of ISE

do not include all of the libraries, drivers, and plugins necessary to communicate with the SMT3-NC (). In order to use the JTAG-SMT3-

NC () with these versions of ISE, version 2.5.2 or higher of the Digilent Plugin for Xilinx Tools (http://store.digilentinc.com/digilent-plugin-

for-xilinx-tools-download-only/) package must be downloaded from the Digilent website and the ISE13 plugin must be manually installed as

described in the included documentation.

In addition to working seamlessly with all Xilinx tools, Digilent’s Adept software (http://store.digilentinc.com/digilent-adept-2-download-

only/) and the Adept software development kit (SDK) support the SMT3-NC () module. For added convenience, customers may freely

download the SDK from Digilent’s website. This Adept software includes a full-featured programming environment and a set of public

application programming interfaces (API ()) that allow user applications to directly drive the JTAG chain.

With the Adept SDK, users can create custom applications that will drive JTAG ports on virtually any device. Please see the Adept SDK

reference manual for more information.

When customers use the JTAG-SMT3-NC () to interface the scan chain of Xilinx’s Zynq platform, they should connect the PS_SRST_B pin

of the SMT3-NC () to the Zynq’s PS_SRST_B pin. This connection allows the Xilinx Tools to reset the Zynq’s processor core at various

times during debugging operations. The PS_SRST_B pin on the SMT3-NC () is driven by an open drain buffer that is capable of sinking up

to 32mA of current. Customers who connect this pin must provide an external pull-up to the appropriate supply rail. A pull-up resistor

between 1K - 100K Ohms is recommended. Please see the following “Application Examples” section for more information.

The VBUS_DETECT pin is used by the USB controller to determine when VBUS is present. When a logic ‘0’ is detected on this pin, the

USB controller is forced into suspend mode. This prevents the SMT3-MC from forcing current down the USB lines when the host or the

hub is powered off. Additionally, it results in reduced current consumption from the module. Connect VBUS to the VBUS_DETECT pin

using a resistor divider, similar to the one in Fig. 3 shown below.

Software Support

PS_SRST_B Pin

VBUS_DETECT Pin