Instruction Manual

XUP Virtex-II Pro Development System www.xilinx.com 31

UG069 (v1.0) March 8, 2005

Using the DIMM Module DDR SDRAM

R

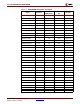

SDRAM_DQ[8] I/O 12 J26 SSTL2-II

SDRAM_DQ[9] I/O 13 G27 SSTL2-II

SDRAM_DQ[10] I/O 19 G28 SSTL2-II

SDRAM_DQ[11] I/O 20 G30 SSTL2-II

SDRAM_DQ[12] I/O 105 L23 SSTL2-II

SDRAM_DQ[13] I/O 106 L24 SSTL2-II

SDRAM_DQ[14] I/O 109 H27 SSTL2-II

SDRAM_DQ[15] I/O 110 H28 SSTL2-II

SDRAM_DQS[1] I/O 14 J29 SSTL2-II

SDRAM_DM[1] 0 107 V29 SSTL2-II

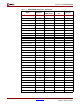

SDRAM_DQ[16] I/O 23 J27 SSTL2-II

SDRAM_DQ[17] I/O 24 J28 SSTL2-II

SDRAM_DQ[18] I/O 28 K29 SSTL2-II

SDRAM_DQ[19] I/O 31 L29 SSTL2-II

SDRAM_DQ[20] I/O 114 N23 SSTL2-II

SDRAM_DQ[21] I/O 117 N24 SSTL2-II

SDRAM_DQ[22] I/O 121 K27 SSTL2-II

SDRAM_DQ[23] I/O 123 K28 SSTL2-II

SDRAM_DQS[2] I/O 25 M30 SSTL2-II

SDRAM_DM[2] 0 119 W29 SSTL2-II

SDRAM_DQ[24] I/O 33 R22 SSTL2-II

SDRAM_DQ[25] I/O 35 M27 SSTL2-II

SDRAM_DQ[26] I/O 39 M28 SSTL2-II

SDRAM_DQ[27] I/O 40 P30 SSTL2-II

SDRAM_DQ[28] I/O 126 P23 SSTL2-II

SDRAM_DQ[29] I/O 127 P24 SSTL2-II

SDRAM_DQ[30] I/O 131 N27 SSTL2-II

SDRAM_DQ[31] I/O 133 N28 SSTL2-II

SDRAM_DQS[3] I/O 36 P29 SSTL2-II

SDRAM_DM[3] 0 129 T22 SSTL2-II

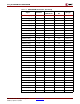

SDRAM_DQ[32] I/O 53 V27 SSTL2-II

Table 2-5: DDR SDRAM Connections (Continued)

Signal Direction

DIMM

Module Pin

FPGA

Pin

I/O Type