User Manual

1-Aug-2012

20

2.6.2 Program Push Button Switch

A PROG push switch, BTN6, toggles EPP PROG_B. This initiates reconfiguring the PL-

subsection by the processor.

2.6.3 Processor Subsystem Reset

Power-on reset, labeled PS_RST/BTN7, erases all debug configurations. The external system

reset allows the user to reset all of the functional logic within the device without disturbing the

debug environment. For example, the previous break points set by the user remain valid after

system reset. Due to security concerns, system reset erases all memory content within the PS,

including the OCM. The PL is also reset in system reset. System reset does not re-sample the

boot mode strapping pins.

2.7 User I/O

2.7.1 User Push Buttons

The ZedBoard provides 7 user GPIO push buttons to the EPP; five on the PL-side and two on the

PS-side.

Pull-downs provide a known default state, pushing each button connects to Vcco.

Table 12 - Push Button Connections

Signal Name

Subsection

Zynq EPP pin

BTNU

PL

T18

BTNR

PL

R18

BTND

PL

R16

BTNC

PL

P16

BTNL

PL

N15

PB1

PS

D13 (MIO 50)

PB2

PS

C10 (MIO 51)

2.7.2 User DIP Switches

The ZedBoard has eight user dip switches, SW0-SW7, providing user input. SPDT switches

connect the I/O through a 10kΩ resistorto the VADJ voltage supply or GND.

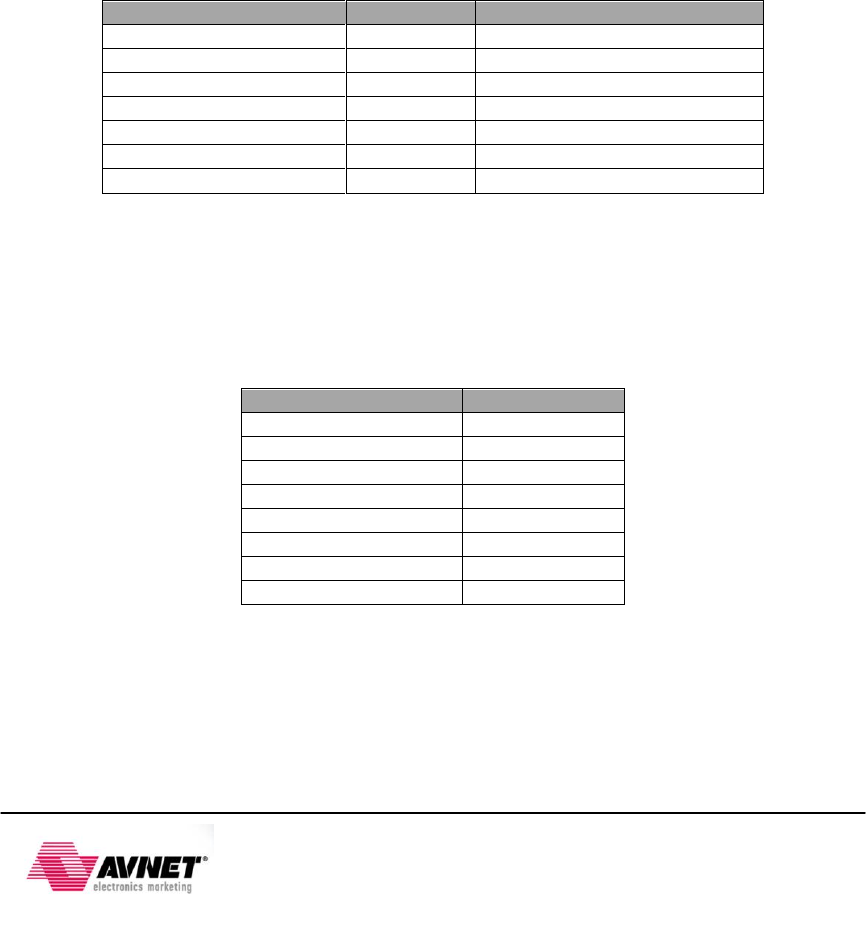

Table 13 - DIP Switch Connections

Signal Name

Zynq EPP pin

SW0

F22

SW1

G22

SW2

H22

SW3

F21

SW4

H19

SW5

H18

SW6

H17

SW7

M15