Data Sheet

Table Of Contents

- 1.0 Device Overview

- 2.0 Can Message Frames

- 3.0 Message Transmission

- 4.0 Message Reception

- 5.0 Bit Timing

- 6.0 Error Detection

- 7.0 Interrupts

- 8.0 Oscillator

- 9.0 RESET

- 10.0 Modes of Operation

- 11.0 Register Map

- 12.0 SPI™ Interface

- 12.1 Overview

- 12.2 Reset Instruction

- 12.3 Read Instruction

- 12.4 Read RX Buffer Instruction

- 12.5 Write Instruction

- 12.6 Load TX Buffer Instruction

- 12.7 Request-To-Send (RTS) Instruction

- 12.8 Read Status Instruction

- 12.9 RX Status Instruction

- 12.10 Bit Modify Instruction

- Figure 12-1: Bit Modify

- Table 12-1: SPI™ Instruction Set

- Figure 12-2: Read instruction

- Figure 12-3: Read RX Buffer Instruction

- Figure 12-4: Byte Write instruction

- Figure 12-5: Load TX Buffer

- Figure 12-6: Request-to-send (RTS) instruction

- Figure 12-7: BIT Modify instruction

- Figure 12-8: Read Status instruction

- Figure 12-9: RX StatUs Instruction

- Figure 12-10: SPI™ Input Timing

- Figure 12-11: SPI™ Output TIming

- 13.0 Electrical Characteristics

- 14.0 PackAging Information

© 2005 Microchip Technology Inc. Preliminary DS21801D-page 73

MCP2515

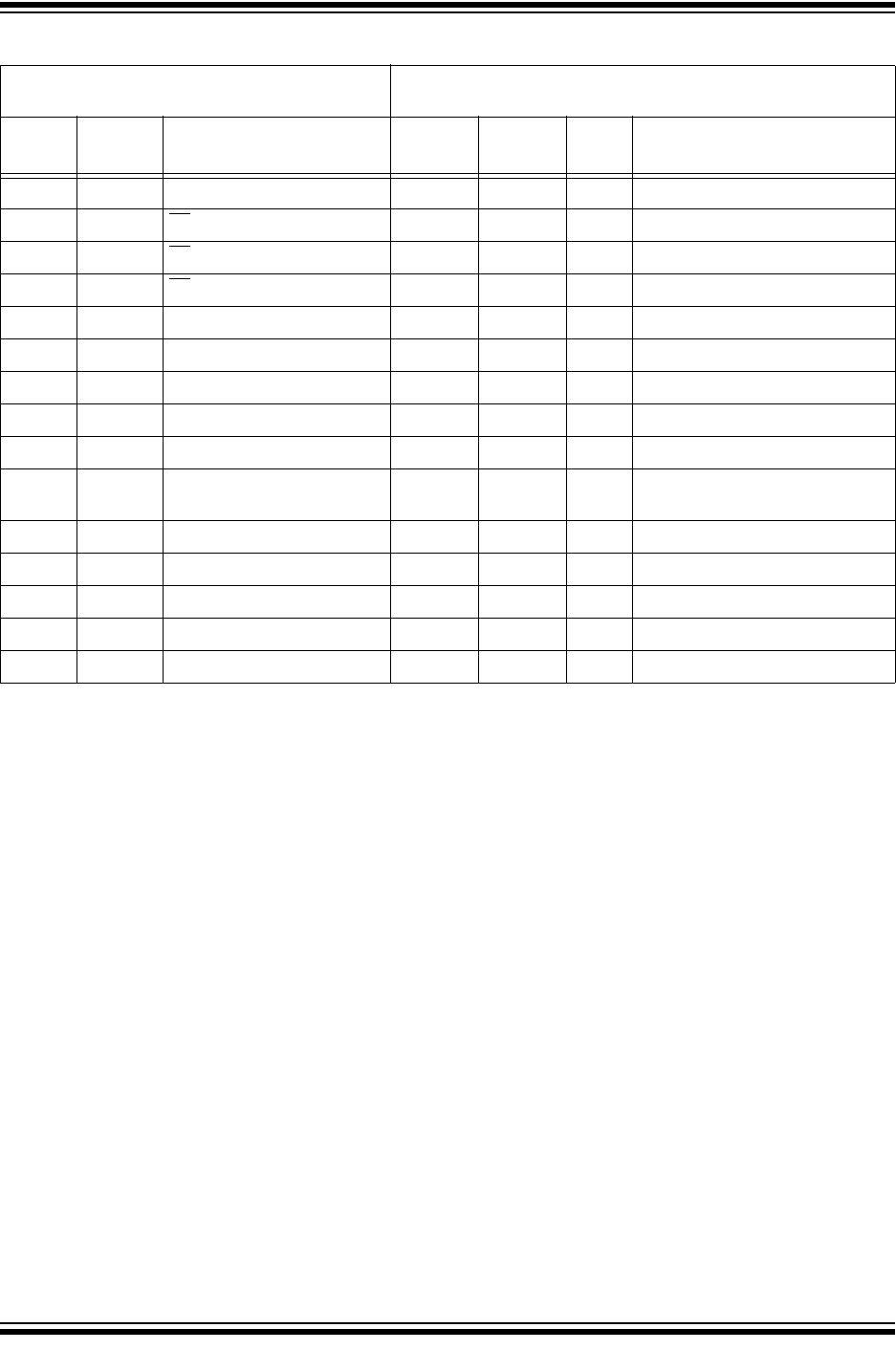

TABLE 13-6: SPI™ INTERFACE AC CHARACTERISTICS

SPI™ Interface AC Characteristics

Industrial (I): T

AMB = -40°C to +85°C VDD = 2.7V to 5.5V

Extended (E): T

AMB = -40°C to +125°C VDD = 4.5V to 5.5V

Param.

No.

Sym Characteristic Min Max Units Conditions

F

CLK Clock Frequency — 10 MHz

1T

CSS CS Setup Time 50 — ns

2T

CSH CS Hold Time 50 — ns

3T

CSD CS Disable Time 50 — ns

4T

SU Data Setup Time 10 — ns

5T

HD Data Hold Time 10 — ns

6T

R CLK Rise Time — 2 µs Note 1

7T

F CLK Fall Time — 2 µs Note 1

8T

HI Clock High Time 45 — ns

9T

LO Clock Low Time 45 — ns

ns

10 T

CLD Clock Delay Time 50 — ns

11 T

CLE Clock Enable Time 50 — ns

12 T

V Output Valid from Clock Low — 45 ns

13 T

HO Output Hold Time 0 — ns

14 T

DIS Output Disable Time — 100 ns

Note 1: This parameter is not 100% tested.