Data Sheet

Table Of Contents

- 1.0 Device Overview

- 2.0 Can Message Frames

- 3.0 Message Transmission

- 4.0 Message Reception

- 5.0 Bit Timing

- 6.0 Error Detection

- 7.0 Interrupts

- 8.0 Oscillator

- 9.0 RESET

- 10.0 Modes of Operation

- 11.0 Register Map

- 12.0 SPI™ Interface

- 12.1 Overview

- 12.2 Reset Instruction

- 12.3 Read Instruction

- 12.4 Read RX Buffer Instruction

- 12.5 Write Instruction

- 12.6 Load TX Buffer Instruction

- 12.7 Request-To-Send (RTS) Instruction

- 12.8 Read Status Instruction

- 12.9 RX Status Instruction

- 12.10 Bit Modify Instruction

- Figure 12-1: Bit Modify

- Table 12-1: SPI™ Instruction Set

- Figure 12-2: Read instruction

- Figure 12-3: Read RX Buffer Instruction

- Figure 12-4: Byte Write instruction

- Figure 12-5: Load TX Buffer

- Figure 12-6: Request-to-send (RTS) instruction

- Figure 12-7: BIT Modify instruction

- Figure 12-8: Read Status instruction

- Figure 12-9: RX StatUs Instruction

- Figure 12-10: SPI™ Input Timing

- Figure 12-11: SPI™ Output TIming

- 13.0 Electrical Characteristics

- 14.0 PackAging Information

MCP2515

DS21801D-page 40 Preliminary © 2005 Microchip Technology Inc.

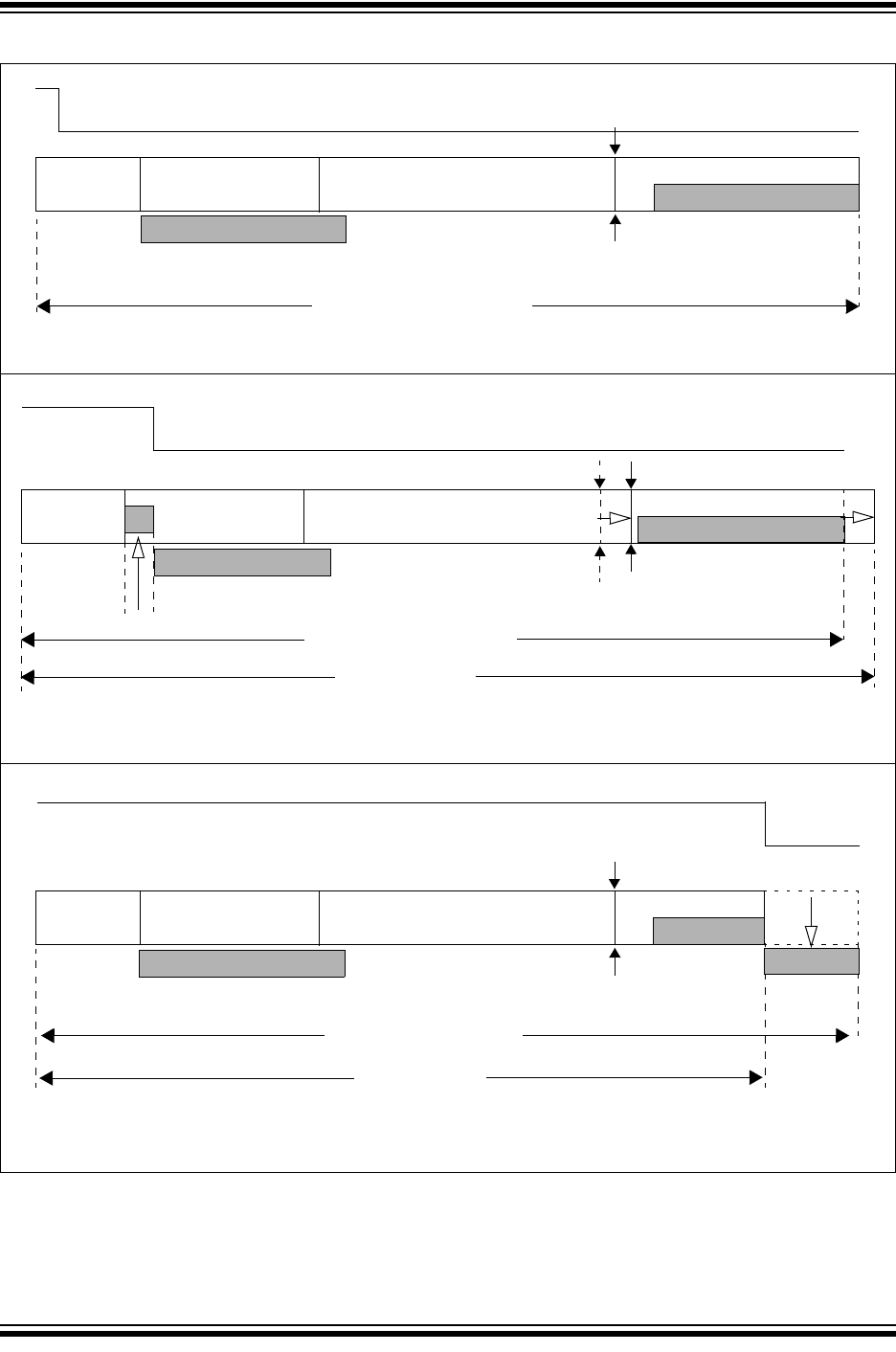

FIGURE 5-3: SYNCHRONIZING THE BIT TIME

SyncSeg

PropSeg

PhaseSeg1 (PS1)

PhaseSeg2 (PS2)

Sample

Point

SyncSeg

PropSeg

PhaseSeg1 (PS1)

PhaseSeg2 (PS2)

Sample

Point

SyncSeg

PropSeg

PhaseSeg1 (PS1)

PhaseSeg2 (PS2)

Sample

Point

Nominal Bit Time (NBT)

SJW (PS1)

SJW (PS2)

Nominal Bit Time (NBT)

SJW (PS1)

SJW (PS2)

Actual Bit Time

Resynchronization to a Slower Transmitter (e > 0)

Input Signal

Input Signal (e < 0)

SJW (PS1)

SJW (PS2)

Nominal Bit Time (NBT)

Actual Bit Time

Resynchronization to a Faster Transmitter (e < 0)

Input Signal (e = 0)

No Resynchronization (e = 0)

(e > 0)