Parallax P2 Edge Module - Datasheet

Table Of Contents

- FEATURES

- HARDWARE

- Pin Descriptions

- Hardware Connections

- Minimal Connections

- External Crystal

- Reset Switch

- SPI Flash Boot Memory

- MicroSD Boot Memory

- Dual Boot Memory

- OPERATION

- SYSTEM ORGANIZATION

- Cogs

- Cog RAM

- Register RAM

- Lookup RAM

- Execution

- Hub

- Hub RAM

- Cog-to-Hub RAM Interface

- System Clock

- CORDIC Solver

- Smart I/O Pins

- Pin Modes

- I/O Pin Circuit

- Equivalent Schematics

- Smart Modes

- PASM2 LANGUAGE IN BRIEF

- Math and Logic

- Pin & Smart Pin

- Branch

- Hub Control, FIFO, & RAM

- Event

- Interrupt

- Register Indirection

- CORDIC Solver

- Color Space Converter and Pixel Mixer

- Lookup Table, Streamer, and Misc

- SYSTEM CHARACTERISTICS

- Absolute Maximum Electrical Ratings

- DC Characteristics

- AC Characteristics

- PACKAGING

- CHANGE LOG

- PARALLAX INCORPORATED

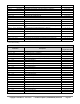

Lookup Table, Streamer, and Misc Instructions

Instruction

Description

Clocks

Cog & LUT / Hub

Lookup Table

RDLUT D,{#}S/P {WC/WZ/WCZ}

Read data from LUT address {#}S/PTRx into D. C = MSB of data. *

3

SETLUTS {#}D

If D[0] = 1 then enable LUT sharing, where LUT writes within the adjacent odd/even companion cog are copied

to this cog's LUT.

2

WRLUT {#}D,{#}S/P

Write D to LUT address {#}S/PTRx.

2

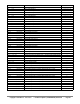

Streamer

GETXACC D

Get the streamer's Goertzel X accumulator into D and the Y accumulator into the next instruction's S, clear

accumulators.

2

SETXFRQ {#}D

Set streamer NCO frequency to D.

2

XCONT {#}D,{#}S

Buer new streamer command to be issued on final NCO rollover of current command, continuing phase.

2+

XINIT {#}D,{#}S

Issue streamer command immediately, zeroing phase.

2

XSTOP

Stop streamer immediately.

2

XZERO {#}D,{#}S

Buer new streamer command to be issued on final NCO rollover of current command, zeroing phase.

2+

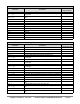

Miscellaneous

AUGD #n

Queue #n to be used as upper 23 bits for next #D occurrence, so that the next 9-bit #D will be augmented to 32

bits.

2

AUGS #n

Queue #n to be used as upper 23 bits for next #S occurrence, so that the next 9-bit #S will be augmented to 32

bits.

2

GETCT D {WC}

Get CT[31:0] or CT[63:32] if WC into D. GETCT WC + GETCT gets full CT. CT=0 on reset, CT++ on every clock. C =

same.

2

GETRND WC/WZ/WCZ

Get RND into C/Z. C = RND[31], Z = RND[30], unique per cog.

2

GETRND D {WC/WZ/WCZ}

Get RND into D/C/Z. RND is the PRNG that updates on every clock. D = RND[31:0], C = RND[31], Z = RND[30],

unique per cog.

2

NOP

No operation.

2

POP D {WC/WZ/WCZ}

Pop stack (K). D = K. C = K[31]. *

2

PUSH {#}D

Push D onto stack.

2

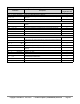

SETQ {#}D

Set Q to D. Use before RDLONG/WRLONG/WMLONG to set block transfer. Also used before

MUXQ/COGINIT/QDIV/QFRAC/QROTATE/WAITxxx.

2

SETQ2 {#}D

Set Q to D. Use before RDLONG/WRLONG/WMLONG to set LUT block transfer.

2

WAITX {#}D {WC/WZ/WCZ}

Wait 2 + D clocks if no WC/WZ/WCZ. If WC/WZ/WCZ, wait 2 + (D & RND) clocks. C/Z = 0.

2 + D

Copyright © Parallax Inc. 2021/05/27 ▪ Parallax Propeller 2 (P2X8C4M64P) Datasheet ▪ Page 43