Parallax P2 Edge Module - Datasheet

Table Of Contents

- FEATURES

- HARDWARE

- Pin Descriptions

- Hardware Connections

- Minimal Connections

- External Crystal

- Reset Switch

- SPI Flash Boot Memory

- MicroSD Boot Memory

- Dual Boot Memory

- OPERATION

- SYSTEM ORGANIZATION

- Cogs

- Cog RAM

- Register RAM

- Lookup RAM

- Execution

- Hub

- Hub RAM

- Cog-to-Hub RAM Interface

- System Clock

- CORDIC Solver

- Smart I/O Pins

- Pin Modes

- I/O Pin Circuit

- Equivalent Schematics

- Smart Modes

- PASM2 LANGUAGE IN BRIEF

- Math and Logic

- Pin & Smart Pin

- Branch

- Hub Control, FIFO, & RAM

- Event

- Interrupt

- Register Indirection

- CORDIC Solver

- Color Space Converter and Pixel Mixer

- Lookup Table, Streamer, and Misc

- SYSTEM CHARACTERISTICS

- Absolute Maximum Electrical Ratings

- DC Characteristics

- AC Characteristics

- PACKAGING

- CHANGE LOG

- PARALLAX INCORPORATED

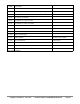

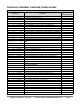

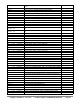

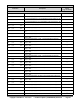

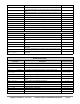

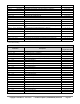

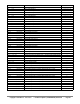

10000

time A-states

10001

time A-highs

10010

time X A-highs/rises/edges -or- timeout on X A-high/rise/edge

10011

for X periods, count time

10100

for X periods, count states

10101

for periods in X+ clocks, count time

10110

for periods in X+ clocks, count states

10111

for periods in X+ clocks, count periods

11000

ADC sample/filter/capture, internally clocked

11001

ADC sample/filter/capture, externally clocked

11010

ADC scope with trigger

11011

1

USB host/device

even/odd pin pair = DM/DP

11100

1

sync serial transmit

A-data, B-clock

11101

sync serial receive

A-data, B-clock

11110

1

async serial transmit

baud rate

11111

async serial receive

baud rate

1

OUT signal overridden

Copyright © Parallax Inc. 2021/05/27 ▪ Parallax Propeller 2 (P2X8C4M64P) Datasheet ▪ Page 32