AutoStore nvSRAM Specification Sheet

Table Of Contents

- Features

- Functional Description

- Pin Configurations

- Device Operation

- SRAM Read

- SRAM Write

- AutoStore Operation

- AutoStore Inhibit mode

- Hardware STORE (HSB) Operation

- Hardware RECALL (Power Up)

- Data Protection

- Noise Considerations

- Hardware Protect

- Low Average Active Power

- Preventing Store

- Best Practices

- Maximum Ratings

- Operating Range

- DC Electrical Characteristics

- Data Retention and Endurance

- Capacitance

- Thermal Resistance

- AC Test Conditions

- AutoStore or Power Up RECALL

- Switching Waveform

- Ordering Information

- Document History Page

- Sales, Solutions, and Legal Information

STK22C48

Document Number: 001-51000 Rev. ** Page 7 of 14

Capacitance

In the following table, the capacitance parameters are listed.

[5]

Parameter Description Test Conditions Max Unit

C

IN

Input Capacitance T

A

= 25°C, f = 1 MHz,

V

CC

= 0 to 3.0V

8pF

C

OUT

Output Capacitance 7pF

Thermal Resistance

In the following table, the thermal resistance parameters are listed.

[5]

Parameter Description Test Conditions

28-SOIC

(300 mil)

28-SOIC

(330 mil)

Unit

Θ

JA

Thermal Resistance

(Junction to Ambient)

Test conditions follow standard test methods

and procedures for measuring thermal

impedance, per EIA / JESD51.

TBD TBD °C/W

Θ

JC

Thermal Resistance

(Junction to Case)

TBD TBD °C/W

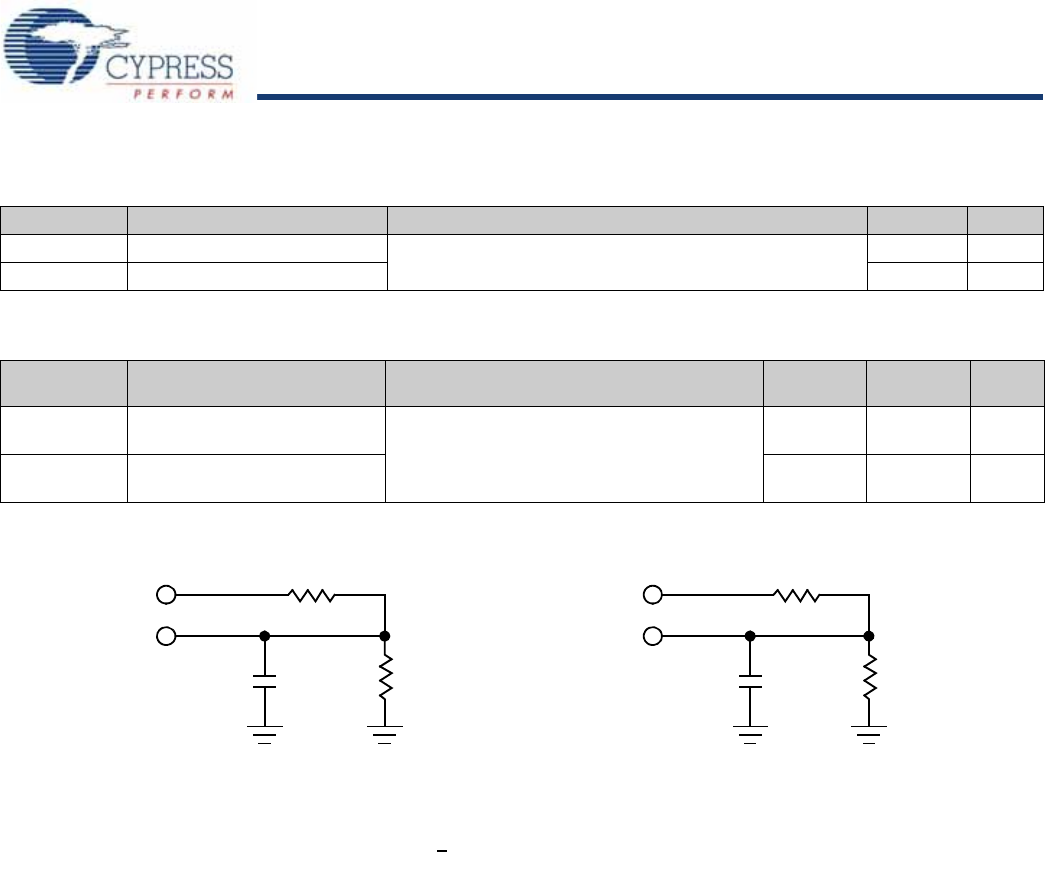

Figure 6. AC Test Loads

AC Test Conditions

5.0V

Output

30 pF

R1 963Ω

R2

512Ω

5.0V

Output

5 pF

R1 963

Ω

R2

512

Ω

For Tri-state Specs

Input Pulse Levels....................................................0V to 3V

Input Rise and Fall Times (10% to 90%)...................... <

5 ns

Input and Output Timing Reference Levels.................... 1.5V

Note

5. These parameters are guaranteed by design and are not tested.

[+] Feedback