AutoStore nvSRAM Specification Sheet

Table Of Contents

- Features

- Functional Description

- Pin Configurations

- Device Operation

- SRAM Read

- SRAM Write

- AutoStore Operation

- AutoStore Inhibit mode

- Hardware STORE (HSB) Operation

- Hardware RECALL (Power Up)

- Data Protection

- Noise Considerations

- Hardware Protect

- Low Average Active Power

- Preventing Store

- Best Practices

- Maximum Ratings

- Operating Range

- DC Electrical Characteristics

- Data Retention and Endurance

- Capacitance

- Thermal Resistance

- AC Test Conditions

- AutoStore or Power Up RECALL

- Switching Waveform

- Ordering Information

- Document History Page

- Sales, Solutions, and Legal Information

STK22C48

Document Number: 001-51000 Rev. ** Page 10 of 14

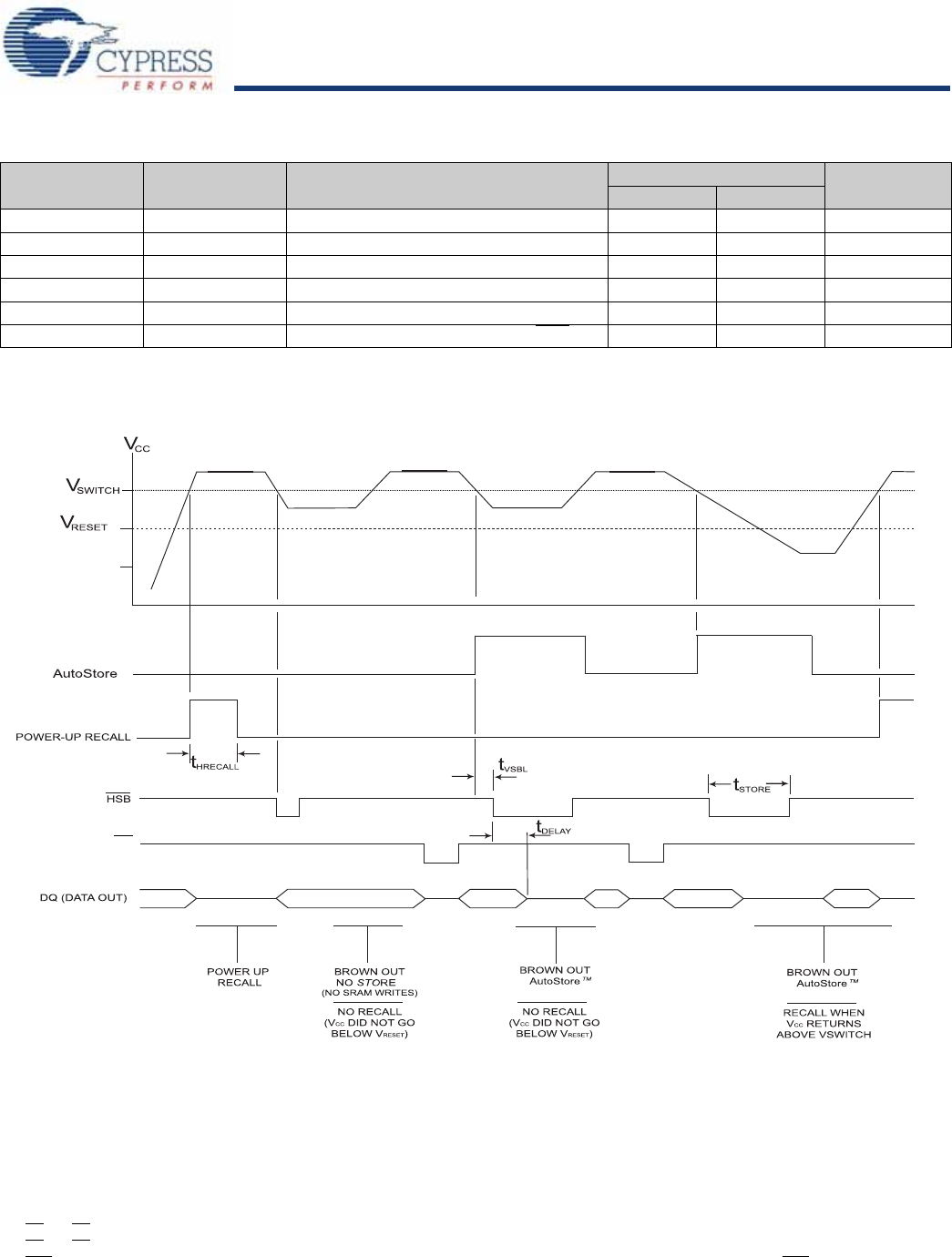

AutoStore or Power Up RECALL

Parameter Alt Description

STK22C48

Unit

Min Max

t

HRECALL

[12]

t

RESTORE

Power up RECALL Duration 550 μs

t

STORE

[14, 15]

t

HLHZ

STORE Cycle Duration 10 ms

t

DELAY

[13]

t

HLQZ ,

t

BLQZ

Time Allowed to Complete SRAM Cycle 1 μs

V

SWITCH

Low Voltage Trigger Level 4.0 4.5 V

V

RESET

Low Voltage Reset Level 3.6 V

t

VSBL

[10]

Low Voltage Trigger (V

SWITCH

) to HSB Low 300 ns

Switching Waveform

Figure 11. AutoStore/Power Up RECALL

WE

Notes

12. t

HRECALL

starts from the time V

CC

rises above V

SWITCH

.

13. CE

and OE low for output behavior.

14. CE

and OE low and WE high for output behavior.

15. HSB

is asserted low for 1us when V

CAP

drops through V

SWITCH

. If an SRAM Write has not taken place since the last nonvolatile cycle, HSB is released and no store

takes place.

[+] Feedback