SoftStore nvSRAM Specification Sheet

Table Of Contents

- Features

- Functional Description

- Logic Block Diagram

- Pin Configurations

- Device Operation

- SRAM Read

- SRAM Write

- Software STORE

- Software RECALL

- Hardware RECALL (Power Up)

- Hardware Protect

- Noise Considerations

- Low Average Active Power

- Best Practices

- Maximum Ratings

- Operating Range

- DC Electrical Characteristics

- Data Retention and Endurance

- Capacitance

- Thermal Resistance

- AC Test Conditions

- Switching Waveforms

- Switching Waveforms

- STORE INHIBIT or Power Up RECALL

- Switching Waveforms

- Software Controlled STORE/RECALL Cycle

- Switching Waveforms

- Part Numbering Nomenclature

- Ordering Information

- Document History Page

- Sales, Solutions and Legal Information

STK11C88

Document Number: 001-50591 Rev. ** Page 5 of 15

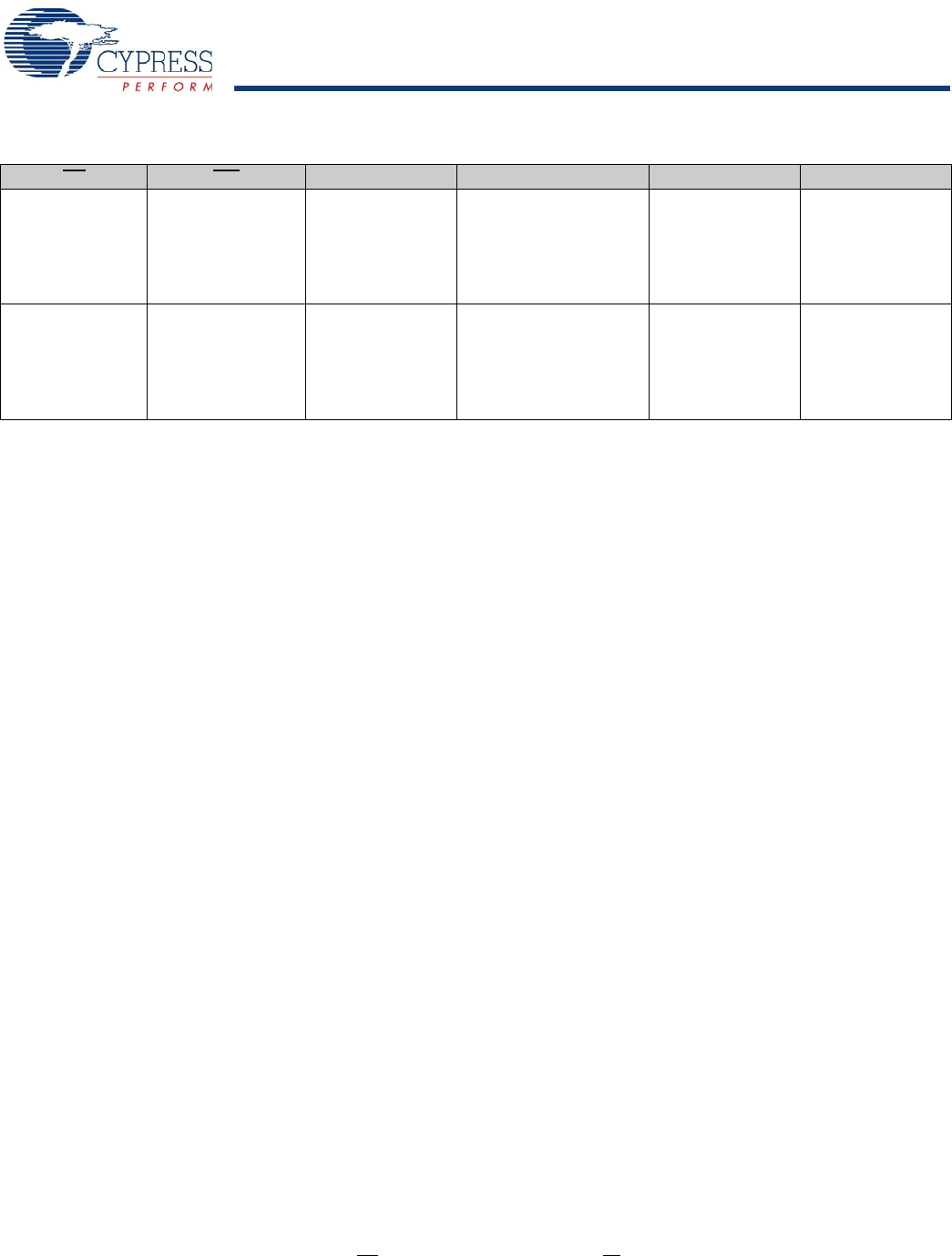

Table 2. Software STORE/RECALL Mode Selection

CE WE

A

13

– A

0

Mode IO Notes

L H 0x0E38

0x31C7

0x03E0

0x3C1F

0x303F

0x0FC0

Read SRAM

Read SRAM

Read SRAM

Read SRAM

Read SRAM

Nonvolatile STORE

Output Data

Output Data

Output Data

Output Data

Output Data

Output Data

[1, 2]

L H 0x0E38

0x31C7

0x03E0

0x3C1F

0x303F

0x0C63

Read SRAM

Read SRAM

Read SRAM

Read SRAM

Read SRAM

Nonvolatile RECALL

Output Data

Output Data

Output Data

Output Data

Output Data

Output Data

[1, 2]

Notes

1. The six consecutive addresses must be in the order listed. WE

must be high during all six consecutive CE controlled cycles to enable a nonvolatile cycle.

2. While there are 15 addresses on the STK11C88, only the lower 14 are used to control software modes.

[+] Feedback