SoftStore nvSRAM Specification Sheet

Table Of Contents

- Features

- Functional Description

- Logic Block Diagram

- Pin Configurations

- Device Operation

- SRAM Read

- SRAM Write

- Software STORE

- Software RECALL

- Hardware RECALL (Power Up)

- Hardware Protect

- Noise Considerations

- Low Average Active Power

- Best Practices

- Maximum Ratings

- Operating Range

- DC Electrical Characteristics

- Data Retention and Endurance

- Capacitance

- Thermal Resistance

- AC Test Conditions

- Switching Waveforms

- Switching Waveforms

- STORE INHIBIT or Power Up RECALL

- Switching Waveforms

- Software Controlled STORE/RECALL Cycle

- Switching Waveforms

- Part Numbering Nomenclature

- Ordering Information

- Document History Page

- Sales, Solutions and Legal Information

STK11C88

Document Number: 001-50591 Rev. ** Page 10 of 15

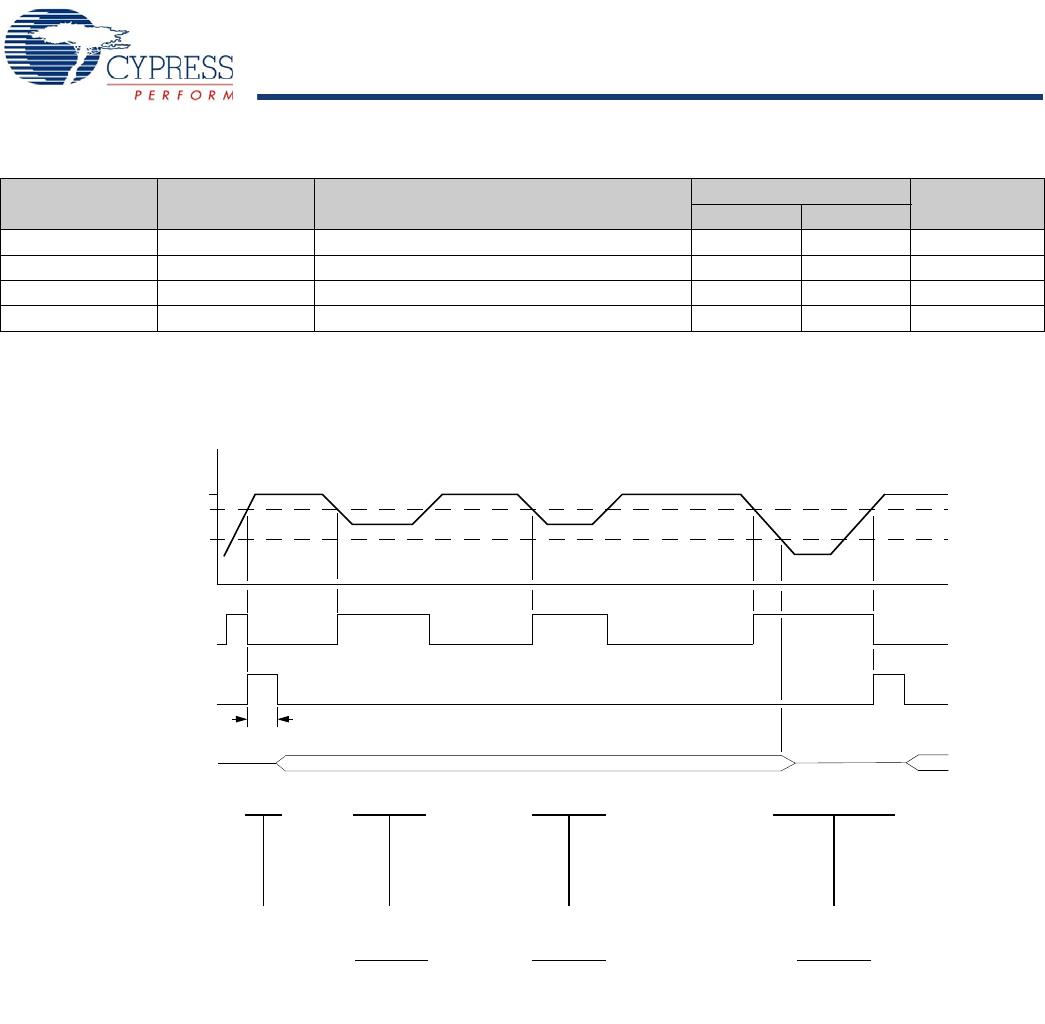

STORE INHIBIT or Power Up RECALL

Parameter Alt Description

STK11C88

Unit

Min Max

t

HRECALL

[10]

t

RESTORE

Power up RECALL Duration 550 μs

t

STORE

[6]

t

HLHZ

STORE Cycle Duration 10 ms

V

RESET

Low Voltage Reset Level 3.6 V

V

SWITCH

Low Voltage Trigger Level 4.0 4.5 V

Switching Waveforms

Figure 9. STORE INHIBIT/Power Up RECALL

V

CC

V

SWITCH

V

RESET

POWER-UP RECALL

DQ (DATA OUT)

STORE INHIBIT

5V

t

HRECALL

POWER-UP

RECALL

BROWN OUT

STORE INHIBIT

NO RECALL

(V

CC

DID NOT GO

BELOW V

RESET

)

BROWN OUT

STORE INHIBIT

NO RECALL

(V

CC

DID NOT GO

BELOW V

RESET

)

BROWN OUT

STORE INHIBIT

RECALL WHEN

V

CC

RETURNS

ABOVE V

SWITCH

Notes

10. t

HRECALL

starts from the time V

CC

rises above V

SWITCH

.

[+] Feedback