QDRTM-II+ SRAM 4-Word Burst Architecture (2.0 Cycle Read Latency) Specification Sheet

Table Of Contents

- Features

- Configurations

- Functional Description

- Selection Guide

- Logic Block Diagram (CY7C1541V18)

- Logic Block Diagram (CY7C1556V18)

- Logic Block Diagram (CY7C1543V18)

- Logic Block Diagram (CY7C1545V18)

- Pin Configuration

- Pin Definitions

- Functional Overview

- Application Example

- Write Cycle Descriptions

- Write Cycle Descriptions

- Write Cycle Descriptions

- IEEE 1149.1 Serial Boundary Scan (JTAG)

- TAP Controller State Diagram

- TAP Controller Block Diagram

- TAP Electrical Characteristics

- TAP AC Switching Characteristics

- TAP Timing and Test Conditions

- Identification Register Definitions

- Scan Register Sizes

- Instruction Codes

- Boundary Scan Order

- Power Up Sequence in QDR-II+ SRAM

- Maximum Ratings

- Operating Range

- Electrical Characteristics

- Capacitance

- Thermal Resistance

- Switching Characteristics

- Switching Waveforms

- Ordering Information

- Package Diagram

- Document History Page

CY7C1541V18, CY7C1556V18

CY7C1543V18, CY7C1545V18

Document Number: 001-05389 Rev. *F Page 3 of 28

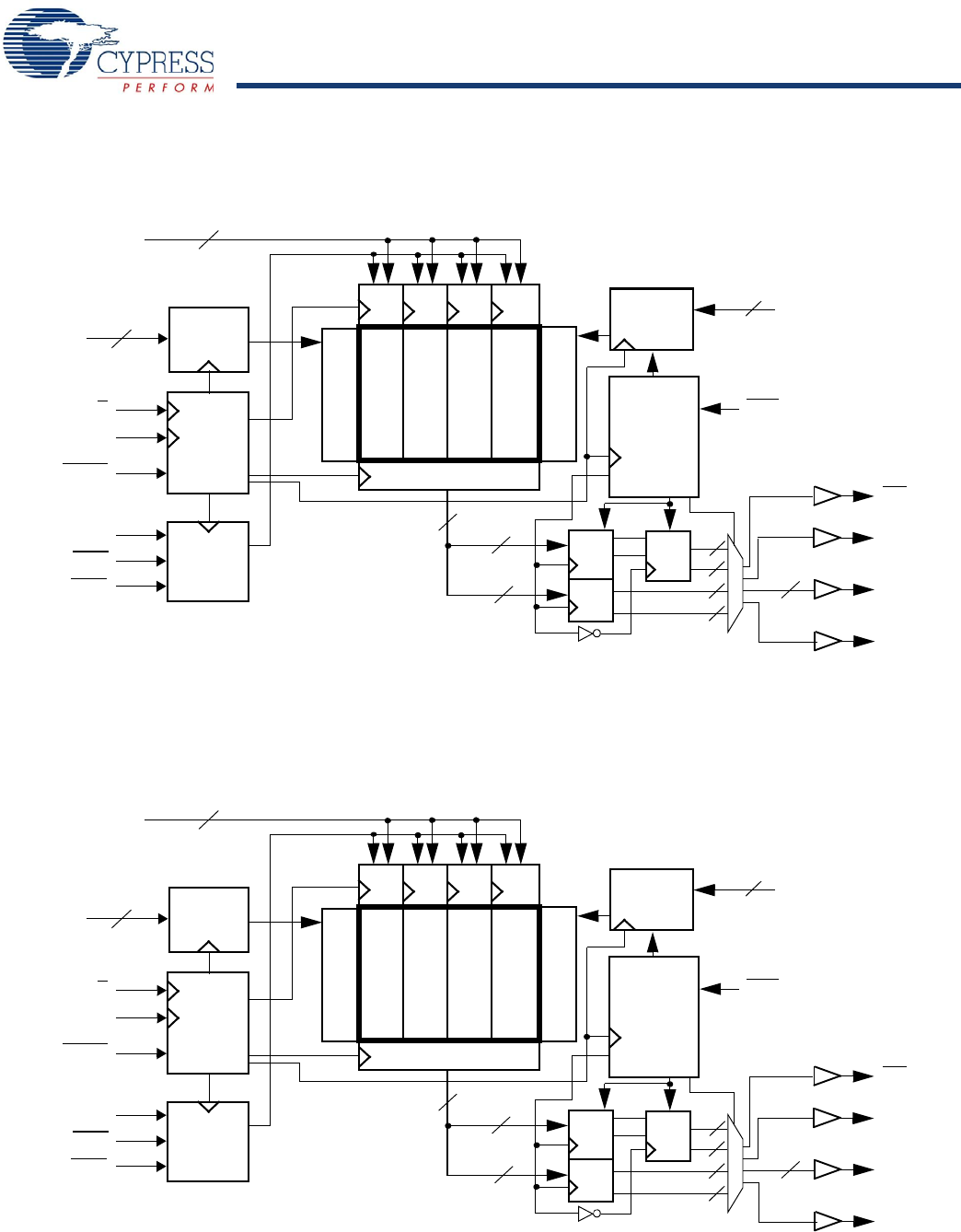

Logic Block Diagram (CY7C1543V18)

Logic Block Diagram (CY7C1545V18)

1M x 18 Array

CLK

A

(19:0)

Gen.

K

K

Control

Logic

Address

Register

D

[17:0]

Read Add. Decode

Read Data Reg.

RPS

WPS

Control

Logic

Address

Register

Reg.

Reg.

Reg.

36

20

72

18

BWS

[1:0]

V

REF

Write Add. Decode

Write

Reg

36

A

(19:0)

20

1M x 18 Array

1M x 18 Array

1M x 18 Array

18

CQ

CQ

DOFF

Q

[17:0]

18

QVLD

18

18

18

Write

Reg

Write

Reg

Write

Reg

512K x 36 Array

CLK

A

(18:0)

Gen.

K

K

Control

Logic

Address

Register

D

[35:0]

Read Add. Decode

Read Data Reg.

RPS

WPS

Control

Logic

Address

Register

Reg.

Reg.

Reg.

72

19

144

36

BWS

[3:0]

V

REF

Write Add. Decode

Write

Reg

72

A

(18:0)

19

512K x 36 Array

512K x 36 Array

512K x 36 Array

36

CQ

CQ

DOFF

Q

[35:0]

36

QVLD

36

36

36

Write

Reg

Write

Reg

Write

Reg

[+] Feedback [+] Feedback