Specifications

Table Of Contents

- Features

- Description

- Logic Block Diagram

- Contents

- Pin Configurations

- Pin Descriptions

- Absolute Maximum Ratings

- DC Characteristics (VCC = 2.7V-3.6V)

- AC Test Conditions

- Capacitance

- RTC DC Characteristics

- SRAM READ Cycles #1 and #2

- SRAM WRITE Cycles #1 and #2

- AutoStore/Power Up RECALL

- Software-Controlled STORE/RECALL Cycle

- Hardware STORE Cycle

- Soft Sequence Commands

- Mode Selection

- nvSRAM Operation

- Real Time Clock

- RTC Register Map

- Commercial and Industrial Ordering Information

- Ordering Codes

- Package Diagram

- Document History Page

- Sales, Solutions, and Legal Information

STK17T88

Document Number: 001-52040 Rev. *C Page 11 of 24

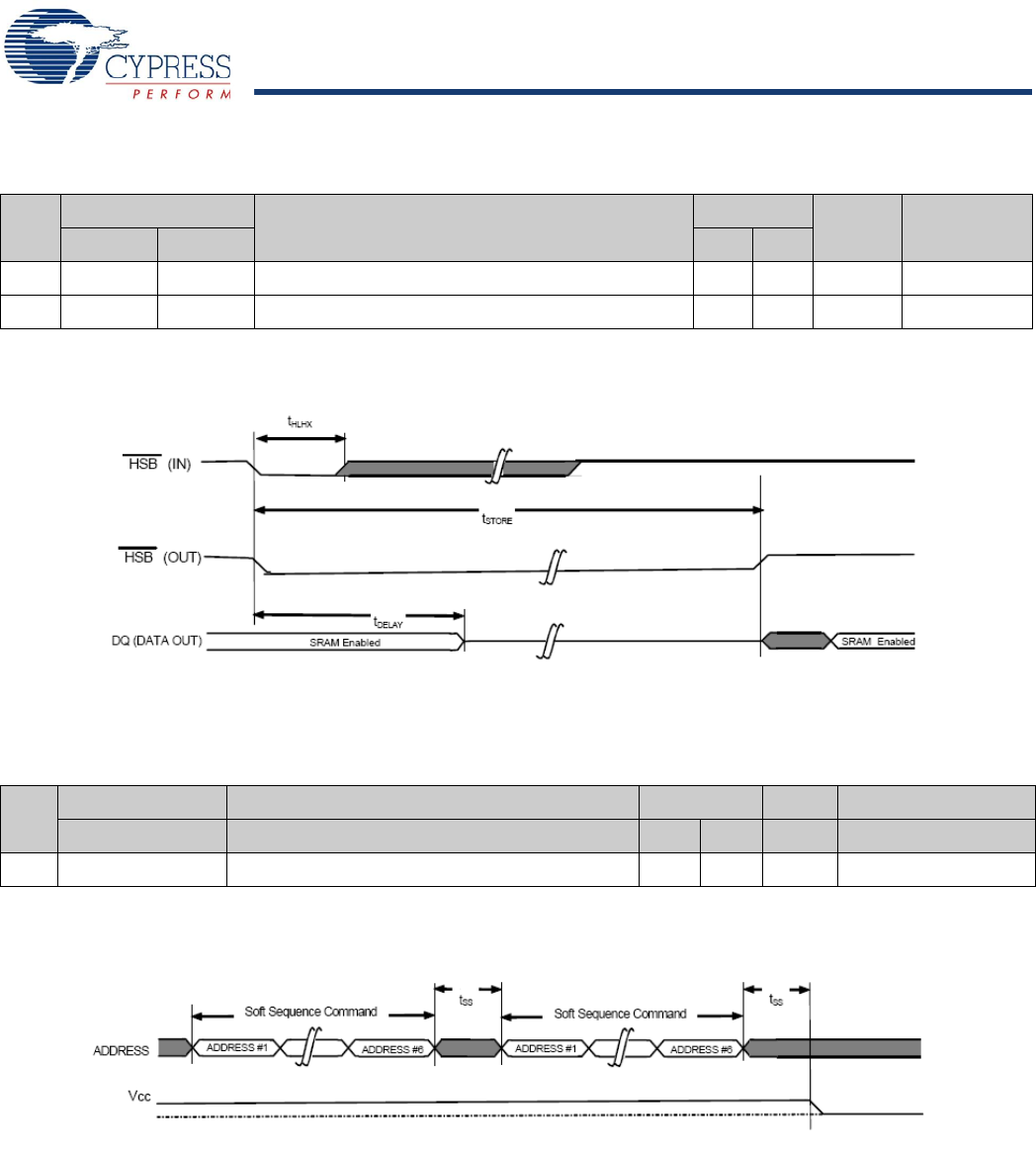

Hardware STORE Cycle

Figure 11. Hardware STORE Cycle

Soft Sequence Commands

Figure 12. Soft Sequence Command

No.

Symbols

Parameter

STK17T88

Units Notes

Standard Alternate Min Max

31 t

DELAY

t

HLQZ

Hardware STORE to SRAM Disabled 1 70 μs14

32 t

HLHX

Hardware STORE Pulse Width 15 ns

32

23

31

No.

Symbol Parameter STK17T88 Units Notes

Standard Min Max

33 t

SS

Soft Sequence Processing Time 70 μs 15, 16

33 33

Notes

14. On a hardware STORE initiation, SRAM operation continues to be enabled for time t

DELAY

to allow read/write cycles to complete

15. This is the amount of time that it takes to take action on a soft sequence command. Vcc power must remain high to effectively register command.

16. Commands such as Store and Recall lock out I/O until operation is complete which further increases this time. See specific command

Not Recommended for New Designs

[+] Feedback