Specifications

Table Of Contents

- Features

- Description

- Logic Block Diagram

- Contents

- Pin Configurations

- Pin Descriptions

- Absolute Maximum Ratings

- DC Characteristics (VCC = 2.7V-3.6V)

- AC Test Conditions

- Capacitance

- RTC DC Characteristics

- SRAM READ Cycles #1 and #2

- SRAM WRITE Cycles #1 and #2

- AutoStore/Power Up RECALL

- Software-Controlled STORE/RECALL Cycle

- Hardware STORE Cycle

- Soft Sequence Commands

- Mode Selection

- nvSRAM Operation

- Real Time Clock

- RTC Register Map

- Commercial and Industrial Ordering Information

- Ordering Codes

- Package Diagram

- Document History Page

- Sales, Solutions, and Legal Information

STK17T88

Document Number: 001-52040 Rev. *C Page 10 of 24

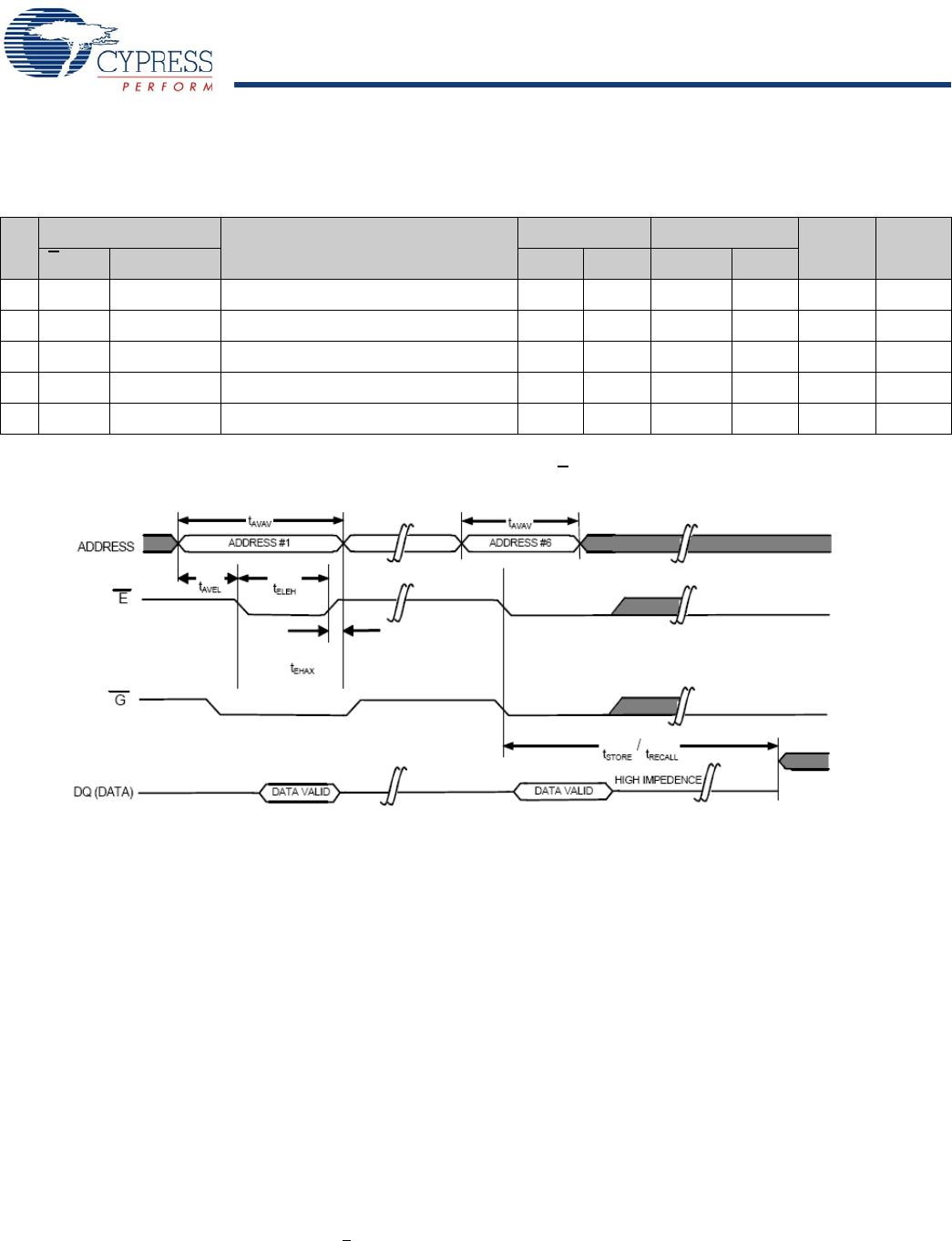

Figure 10. Software Store/Recall Cycle: E CONTROLLED

[13]

Software-Controlled STORE/RECALL Cycle

In the following table, the software controlled STORE and RECALL cycle parameters are listed.

[12, 13]

No.

Symbols

Parameter

STK17T88-35 STK17T88-45

Units Notes

E Cont Alternate Min Max Min Max

26 t

AVAV

t

RC

STORE/RECALL Initiation Cycle Time 25 45 ns 13

27 t

AVEL

t

AS

Address Setup Time 0 0 ns

28 t

ELEH

t

CW

Clock Pulse Width 20 30 ns

29 t

EHAX

Address Hold Time 1 1 ns

30 t

RECALL

RECALL Duration 100 100 us

26

26

27

28

29

23 30

Notes

12. The software sequence is clocked on the falling edge of E

controlled READs

13. The six consecutive addresses must be read in the order listed in the Mode Selection table. W must be high during all six consecutive cycles.

Not Recommended for New Designs

[+] Feedback