nvSRAM Specification Sheet

Table Of Contents

- Features

- Description

- Logic Block Diagram

- Pin Configurations

- Pin Descriptions

- Absolute Maximum Ratings

- DC Characteristics

- (VCC = 2.7V-3.6V)

- AC Test Conditions

- Capacitance

- RTC DC Characteristics

- SRAM READ Cycles #1 and #2

- SRAM WRITE Cycles #1 and #2

- AutoStore/Power Up RECALL

- Software-Controlled STORE/RECALL Cycle

- Hardware STORE Cycle

- Soft Sequence Commands

- MODE Selection

- nvSRAM Operation

- Real Time Clock

- RTC Register Map

- Commercial and Industrial Ordering Information

- Ordering Codes

- Package Diagram

- Document History Page

- Sales, Solutions, and Legal Information

STK17T88

Document Number: 001-52040 Rev. *A Page 8 of 22

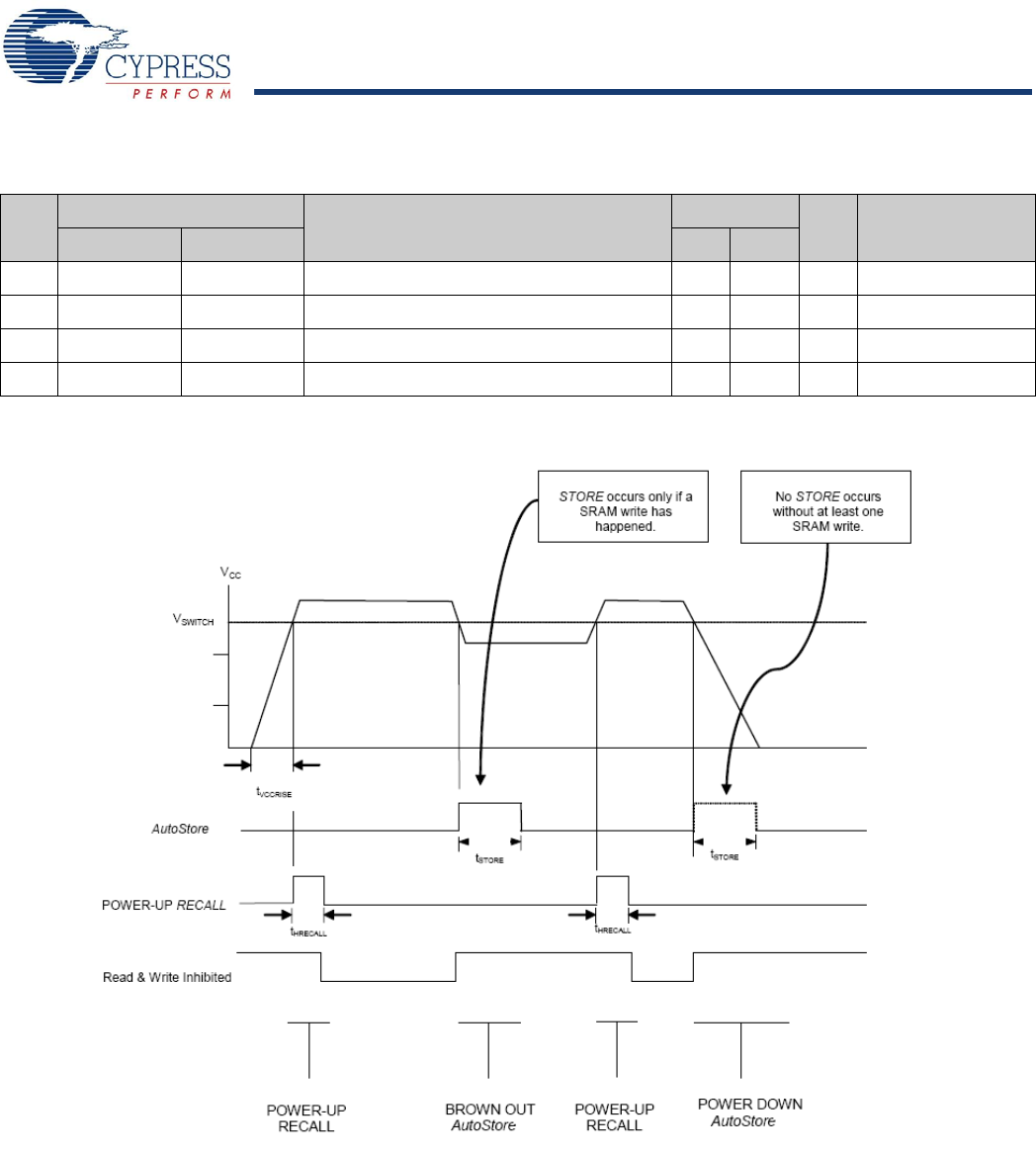

AutoStore/Power Up RECALL

Figure 9. AutoStore Power Up RECALL

Notes

9. t

HRECALL

starts from the time V

CC

rises above V

SWITCH

10. If an SRAM WRITE has not taken place since the last nonvolatile cycle, no STORE will take place

11. Industrial Grade Devices require 15 ms Max.

NO.

Symbols

Parameter

STK17T88

Units Notes

Standard Alternate Min Max

22 t

HRECALL

Power up RECALL Duration 40 ms 9

23 t

STORE

t

HLHZ

STORE Cycle Duration 12.5 ms 10, 11

24 V

SWITCH

Low Voltage Trigger Level 2.65 V

25 V

CCRISE

V

CC

Rise Time 150 µS

NOTE: Read and Write cycles will be ignored during STORE, RECALL and while V

CC

is below V

SWITCH

25

23 23

22

22

[+] Feedback