User's Manual

CRXi

µ

µµ

µ

Core Module

CR

µ

µµ

µ

X Logic,

2001 all rights reserved

5

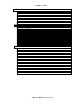

PIN DESCRIPTION

1 VCC – 5 VDC power input

2 P10 - U1 port 1.0 general purpose I/O or external I/O for timer/counter 2

3 P11 - U1 port 1.1 general purpose I/O or timer/counter 2 capture/reload trigger

4 P12 - U1 port 1.2 general purpose I/O or serial port 1 input

5 P13 - U1 port 1.3 general purpose I/O or serial port 1 output

6 P14 - U1 port 1.4 general purpose I/O or external interrupt 2 (positive edge detect)

7 P15 - U1 port 1.5 general purpose I/O or external interrupt 3 (negative edge detect)

8 P16 - U1 port 1.6 general purpose I/O or external interrupt 4 (positive edge detect)

9 P17 - U1 port 1.7 general purpose I/O or external interrupt 5 (negative edge detect)

10 NC

11 P30 - U1 port 3.0 general purpose I/O or serial port 0 input (RXD0)

12 P31 - U1 port 3.1 general purpose I/O or serial port 0 output (TXD0)

13 P32 - U1 port 3.2 general purpose I/O or external interrupt 0

14 P33 - U1 port 3.3 general purpose I/O or external interrupt 1

15 P43 - U1 port 3.4 general purpose I/O or timer 0 external input

16 P35 - U1 port 3.5 general purpose I/O or timer 1 external input

17 /WR – active low write line from U1

18 /RD – active low read line from U1

19 /RESET – system reset – a logic low on this pin resets U1 and U2

20 GND

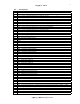

21 AD0 – multiplexed address/data bus

22 AD1 – multiplexed address/data bus

23 AD2 – multiplexed address/data bus

24 AD3 – multiplexed address/data bus

25 AD4 – multiplexed address/data bus

26 AD5 – multiplexed address/data bus

27 AD6 – multiplexed address/data bus

28 AD7 – multiplexed address/data bus

29 A8 – address bus, high byte

30 A9 – address bus, high byte

31 A10 – address bus, high byte

32 A11 – address bus, high byte

33 A12 – address bus, high byte

34 A13 – address bus, high byte

35 A14 – address bus, high byte

36 A15 – address bus, high byte

37 VCC – 5 VDC power input

38 PC2 – U2 general purpose I/O

39 PA0 – latched low order address byte

40 PA1 – latched low order address byte

41 PA2 – latched low order address byte

42 PA3 – latched low order address byte

43 PA4 – latched low order address byte

44 PA5 – latched low order address byte

45 PA6 – latched low order address byte

46 PA7 – latched low order address byte

47 PB0 – U2 general purpose I/O – optional CS3 active high chip select (addresses 8B00h – 8BFFh)

48 PB1 – U2 general purpose I/O – optional CS4 active high chip select (addresses 8C00h – 8CFFh)

49 PB2 – U2 general purpose I/O – optional CS5 active low chip select (addresses 8D00h – 8DFFh)

50 PB3 – U2 general purpose I/O – optional CS6 active low chip select (addresses 8E00h – 8EFFh)

51 /CS0 – active low external chip select (addresses 8800h – 88FFh)

52 /CS1 – active low external chip select (addresses 8900h – 89FFh)

53 /CS2 – active low external chip select (addresses 8A00h – 8AFFh)