User Manual

Table Of Contents

- AD-1192 Instruction cover.pdf

- AD-1192 Instruction Manual.pdf

- AD-1192 Instruction cover.pdf

- AD-1192 Instruction Manual.pdf

- WEEE MARK

- CE Marking Declaration of Conformity

- FCC Declaration of Conformity

- Compliance Statements

- SAFETY PRECAUTIONS

- THE TABLE OF CONTENTS

- 1. INTRODUCTION

- 2. TYPE CLASSIFICATIONS

- 3. EXTERNAL APPEARANCE AND PART DESCRIPTIONS

- 4. OPERATIONS

- 5. PARALLEL INTERFACE

- 6. SERIAL INTERFACE

- 7. DIP SWITCH SETTING

- 8. PRINT CONTROL FUNCTION

- 9. CHARACTER CODE TABLE

- 9.1 ASCII + 910 Emulation (International)

- 9.2 910 Emulation (Japan)

- 9.3 Codepage PC437 (USA, Standard Europe)

- 9.4 Katakana

- 9.5 Codepage PC858 (Multilingual)

- 9.6 Codepage PC860 (Portuguese)

- 9.7 Codepage PC863 (Canadian-French)

- 9.8 Codepage PC865 (Nordic)

- 9.9 Codepage PC852 (Eastern Europe)

- 9.10 Codepage PC866 (Russian)

- 9.11 Codepage PC857 (Turkish)

- 9.12 Codepage WPC1252 (Windows Latin1)

- 9.13 Codepage PC864 (Arabic)

- 9.14 Codepage PC869 (Greek)

- 9.15 International Character Code Table

- 10. EXTERNAL DIMENSIONS

— 25 —

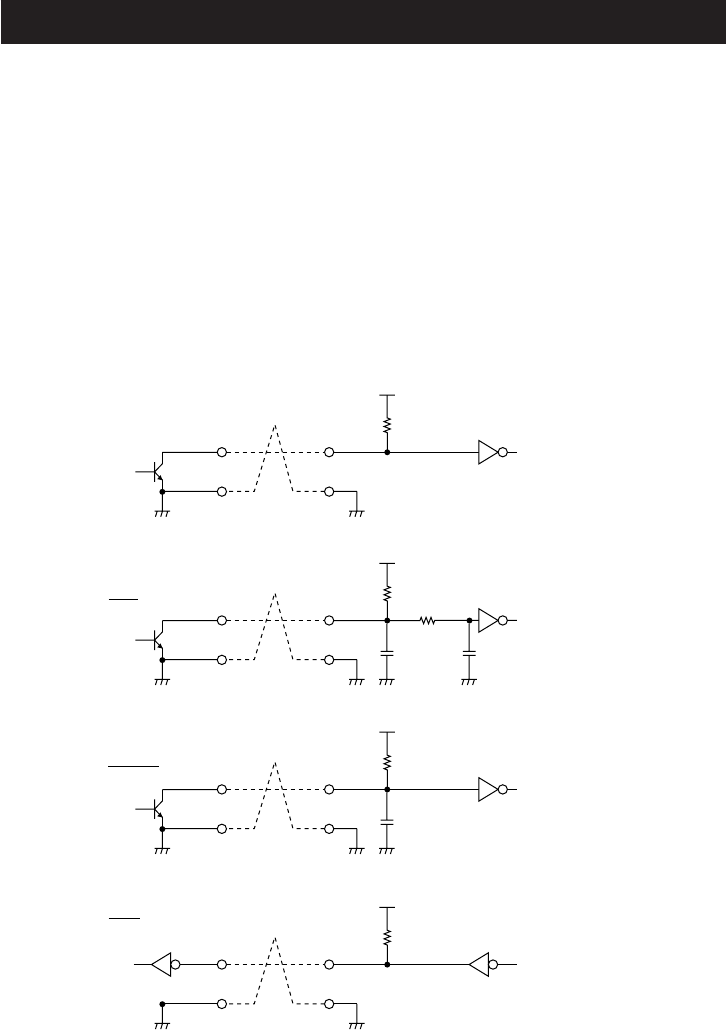

DATA

VCC

3.3k

< HOST SIDE > < PRINTER SIDE >

(HC04 or equivalent)

STB

ACK BUSY P.N.E.

OUTPUT SIGNAL

RESET

VCC

3.3k

100

102 471

(HC04 or equivalent)

VCC

3.3k

104

(HC04 or equivalent)

VCC

3.3k

(HC04 or equivalent)

5.4 Electrical Characteristics

(1) Input signal level

All inputs are HCMOS level. As the input side is pulled up with a resistance of 3.3

kΩ, it can be used at TTL level.

TTL Level HCMOS Level

“HIGH” level: 2.0 V MIN “HIGH” level: 4.0 V MIN

“LOW” level: 0.8 V MAX “LOW” level: 1.0 V MAX

(2) Output signal level

Output signal level is held at TTL.

(3) I/O conditions