User Manual

Table Of Contents

- Features

- Description

- 1. Pin Out - 144-Pin LQFP Package

- 2. Pin Out - 160-Ball FBGA Package

- 3. Pin Descriptions

- 4. operation

- 5. Power-up

- 6. Master Clock

- 7. G.772 Monitoring

- 8. Building Integrated Timing Systems (BITS) Clock Mode

- 9. Transmitter

- 10. Receiver

- 11. Jitter Attenuator

- 12. Operational Summary

- 13. Host Mode

- 14. Register Descriptions

- 14.1 Revision/IDcode Register (00h)

- 14.2 Analog Loopback Register (01h)

- 14.3 Remote Loopback Register (02h)

- 14.4 TAOS Enable Register (03h)

- 14.5 LOS Status Register (04h)

- 14.6 DFM Status Register (05h)

- 14.7 LOS Interrupt Enable Register (06h)

- 14.8 DFM Interrupt Enable Register (07h)

- 14.9 LOS Interrupt Status Register (08h)

- 14.10 DFM Interrupt Status Register (09h)

- 14.11 Software Reset Register (0Ah)

- 14.12 Performance Monitor Register (0Bh)

- 14.13 Digital Loopback Reset Register (0Ch)

- 14.14 LOS/AIS Mode Enable Register (0Dh)

- 14.15 Automatic TAOS Register (0Eh)

- 14.16 Global Control Register (0Fh)

- 14.17 Line Length Channel ID Register (10h)

- 14.18 Line Length Data Register (11h)

- 14.19 Output Disable Register (12h)

- 14.20 AIS Status Register (13h)

- 14.21 AIS Interrupt Enable Register (14h)

- 14.22 AIS Interrupt Status Register (15h)

- 14.23 AWG Broadcast Register (16h)

- 14.24 AWG Phase Address Register (17h)

- 14.25 AWG Phase Data Register (18h)

- 14.26 AWG Enable Register (19h)

- 14.27 Reserved Register (1Ah)

- 14.28 Reserved Register (1Bh)

- 14.29 Reserved Register (1Ch)

- 14.30 Reserved Register (1Dh)

- 14.31 Bits Clock Enable Register (1Eh)

- 14.32 Reserved Register (1Fh)

- 14.33 Status Registers

- 15. Arbitrary Waveform Generator

- 16. JTAG Support

- 17. Boundary Scan Register (BSR)

- 18. Applications

- 19. Characteristics and specifications

- 19.1 Absolute Maximum Ratings

- 19.2 Recommended Operating Conditions

- 19.3 Digital Characteristics

- 19.4 Transmitter Analog Characteristics

- 19.5 Receiver Analog Characteristics

- 19.6 Jitter Attenuator Characteristics

- 19.7 Master Clock Switching Characteristics

- 19.8 Transmit Switching Characteristics

- 19.9 Receive Switching Characteristics

- 19.10 Switching Characteristics - Serial Port

- 19.11 Switching Characteristics - Parallel Port (Multiplexed Mode)

- 19.12 Switching Characteristics- Parallel Port (Non-Multiplexed Mode)

- 19.13 Switching Characteristics - JTAG

- 20. Compliant Recommendations and specifications

- 21. 160-Ball FBGA package dimensions

- 22. 144-Pin LQFP Package dimensions

CS61880

DS450PP3 7

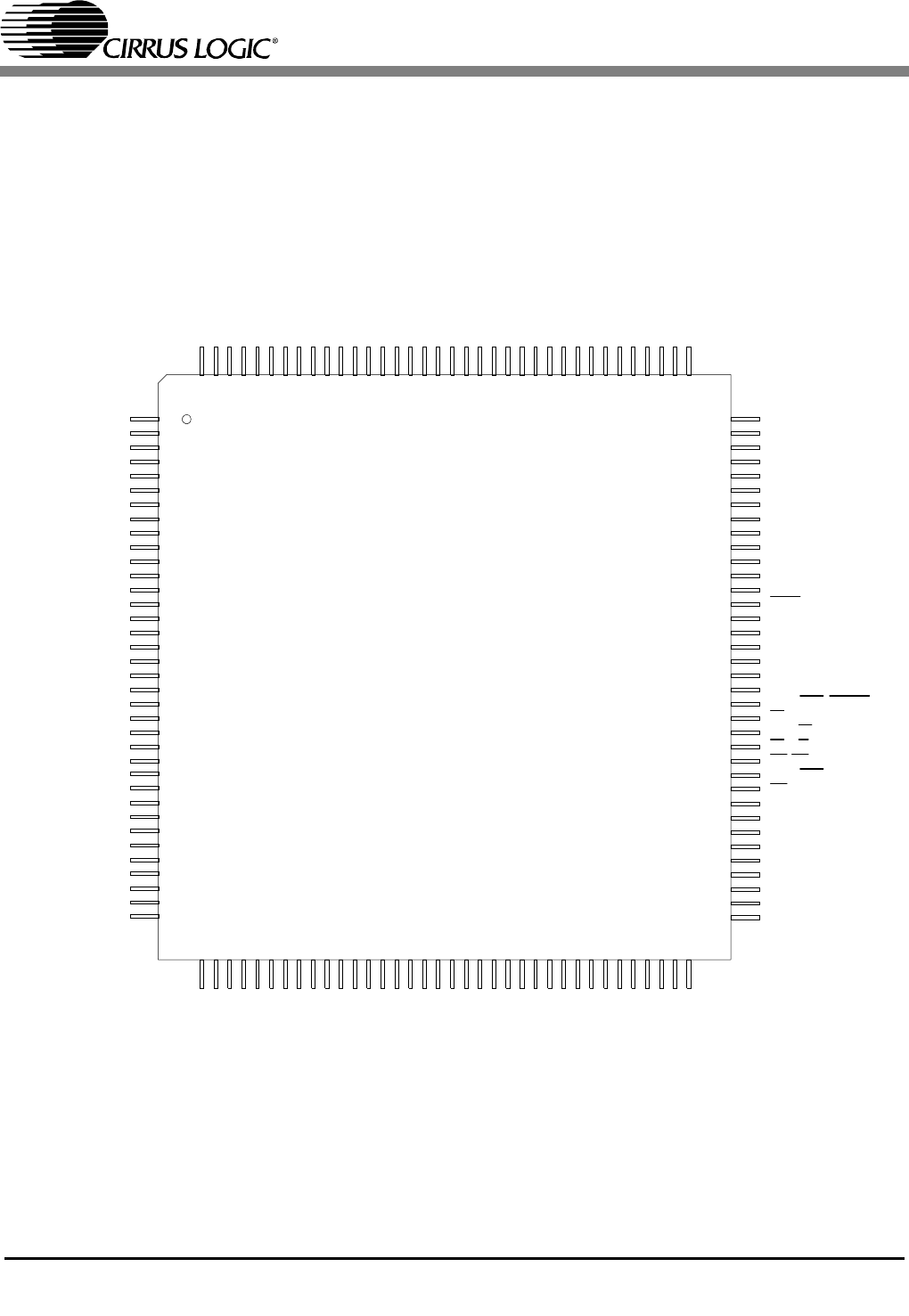

1. PIN OUT - 144-PIN LQFP PACKAGE

144

143

142

140

139

138

137

136

135

141

134

133

132

131

130

129

128

127

126

125

124

123

122

121

120

CS61880

144-Pin

LQFP

37

38

39

41

42

43

44

45

46

40

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

108

107

106

104

103

102

101

100

99

105

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

119

118

117

116

115

114

113

112

111

110

109

1

2

3

5

6

7

8

9

10

4

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

TNEG7/UBS7

RCLK7

RPOS7/RDATA7

RNEG7/BPV7

LOS7

RTIP7

RRING7

TV+7

TTIP7

TRING7

TGND7

RRING6

RTIP6

TGND6

TRING6

TTIP6

TV+6

RTIP5

RRING5

TV+5

TTIP5

TRING5

TGND5

RRING4

RTIP4

TGND4

TRING4

TTIP4

TV+4

CLKE

TXOE

LOS4

RNEG4/BPV4

RPOS4/RDATA4

RCLK4

TNEG4/UBS4

TPOS7/TDATA7

TCLK7

LOS6

RNEG6/BPV6

RPOS6/RDATA6

RCLK6

TNEG6/UBS6

TPOS6/TDATA6

TCLK6

MCLK

MODE

A4

A3

A2

A1

A0

VCCIO

GNDIO

RV0+

RGND0

LOOP0/D0

LOOP1/D1

LOOP2/D2

LOOP3/D3

LOOP4/D4

LOOP5/D5

LOOP6/D6

LOOP7/D7

TCLK1

TPOS1/TDATA1

TNEG1/UBS1

RCLK1

RPOS1/RDATA1

RNEG1/BPV1

LOS1

TCLK0

TPOS0/TDATA0

TNEG0/USB0

RCLK0

RPOS0/RDATA0

RNEG0/BPV0

LOS0

MUX/BITSEN0

TV+0

TTIP0

TRING0

TGND0

RTIP0

RRING0

TGND1

TRING1

TTIP1

TV+1

RRING1

RTIP1

TV+2

TTIP2

TRING2

TGND2

RTIP2

RRING2

TGND3

TRING3

TTIP3

TV+3

RRING3

RTIP3

LOS3

RNEG3/RBPV3

RPOS3/RDATA3

RCLK3

TNEG3/UBS3

(Top View)

TPOS4/TDATA4

TCLK4

LOS5

RNEG5/BPV5

RPOS5/RDATA5

RCLK5

TNEG5/UBS5

TPOS5/TDATA5

TCLK5

TDI

TDO

TCK

TMS

TRST

REF

CBLSEL

VCCIO

GNDIO

RV1+

RGND1

INTL/MOT/CODEN

CS/JASEL

ALE/AS/SCLK

RD/RW

WR/DS/SDI

RDY/ACK/SDO

INT

TCLK2

TPOS2/TDATA2

TNEG2/UBS2

RCLK2

RPOS2/RDATA2

RNEG2/BPV2

LOS2

TCLK3

TPOS3/TDATA3

Figure 1. CS61880 144-Pin LQFP Package Pin Outs