User Manual

Table Of Contents

- Features

- Description

- 1. Pin Out - 144-Pin LQFP Package

- 2. Pin Out - 160-Ball FBGA Package

- 3. Pin Descriptions

- 4. operation

- 5. Power-up

- 6. Master Clock

- 7. G.772 Monitoring

- 8. Building Integrated Timing Systems (BITS) Clock Mode

- 9. Transmitter

- 10. Receiver

- 11. Jitter Attenuator

- 12. Operational Summary

- 13. Host Mode

- 14. Register Descriptions

- 14.1 Revision/IDcode Register (00h)

- 14.2 Analog Loopback Register (01h)

- 14.3 Remote Loopback Register (02h)

- 14.4 TAOS Enable Register (03h)

- 14.5 LOS Status Register (04h)

- 14.6 DFM Status Register (05h)

- 14.7 LOS Interrupt Enable Register (06h)

- 14.8 DFM Interrupt Enable Register (07h)

- 14.9 LOS Interrupt Status Register (08h)

- 14.10 DFM Interrupt Status Register (09h)

- 14.11 Software Reset Register (0Ah)

- 14.12 Performance Monitor Register (0Bh)

- 14.13 Digital Loopback Reset Register (0Ch)

- 14.14 LOS/AIS Mode Enable Register (0Dh)

- 14.15 Automatic TAOS Register (0Eh)

- 14.16 Global Control Register (0Fh)

- 14.17 Line Length Channel ID Register (10h)

- 14.18 Line Length Data Register (11h)

- 14.19 Output Disable Register (12h)

- 14.20 AIS Status Register (13h)

- 14.21 AIS Interrupt Enable Register (14h)

- 14.22 AIS Interrupt Status Register (15h)

- 14.23 AWG Broadcast Register (16h)

- 14.24 AWG Phase Address Register (17h)

- 14.25 AWG Phase Data Register (18h)

- 14.26 AWG Enable Register (19h)

- 14.27 Reserved Register (1Ah)

- 14.28 Reserved Register (1Bh)

- 14.29 Reserved Register (1Ch)

- 14.30 Reserved Register (1Dh)

- 14.31 Bits Clock Enable Register (1Eh)

- 14.32 Reserved Register (1Fh)

- 14.33 Status Registers

- 15. Arbitrary Waveform Generator

- 16. JTAG Support

- 17. Boundary Scan Register (BSR)

- 18. Applications

- 19. Characteristics and specifications

- 19.1 Absolute Maximum Ratings

- 19.2 Recommended Operating Conditions

- 19.3 Digital Characteristics

- 19.4 Transmitter Analog Characteristics

- 19.5 Receiver Analog Characteristics

- 19.6 Jitter Attenuator Characteristics

- 19.7 Master Clock Switching Characteristics

- 19.8 Transmit Switching Characteristics

- 19.9 Receive Switching Characteristics

- 19.10 Switching Characteristics - Serial Port

- 19.11 Switching Characteristics - Parallel Port (Multiplexed Mode)

- 19.12 Switching Characteristics- Parallel Port (Non-Multiplexed Mode)

- 19.13 Switching Characteristics - JTAG

- 20. Compliant Recommendations and specifications

- 21. 160-Ball FBGA package dimensions

- 22. 144-Pin LQFP Package dimensions

CS61880

34 DS450PP3

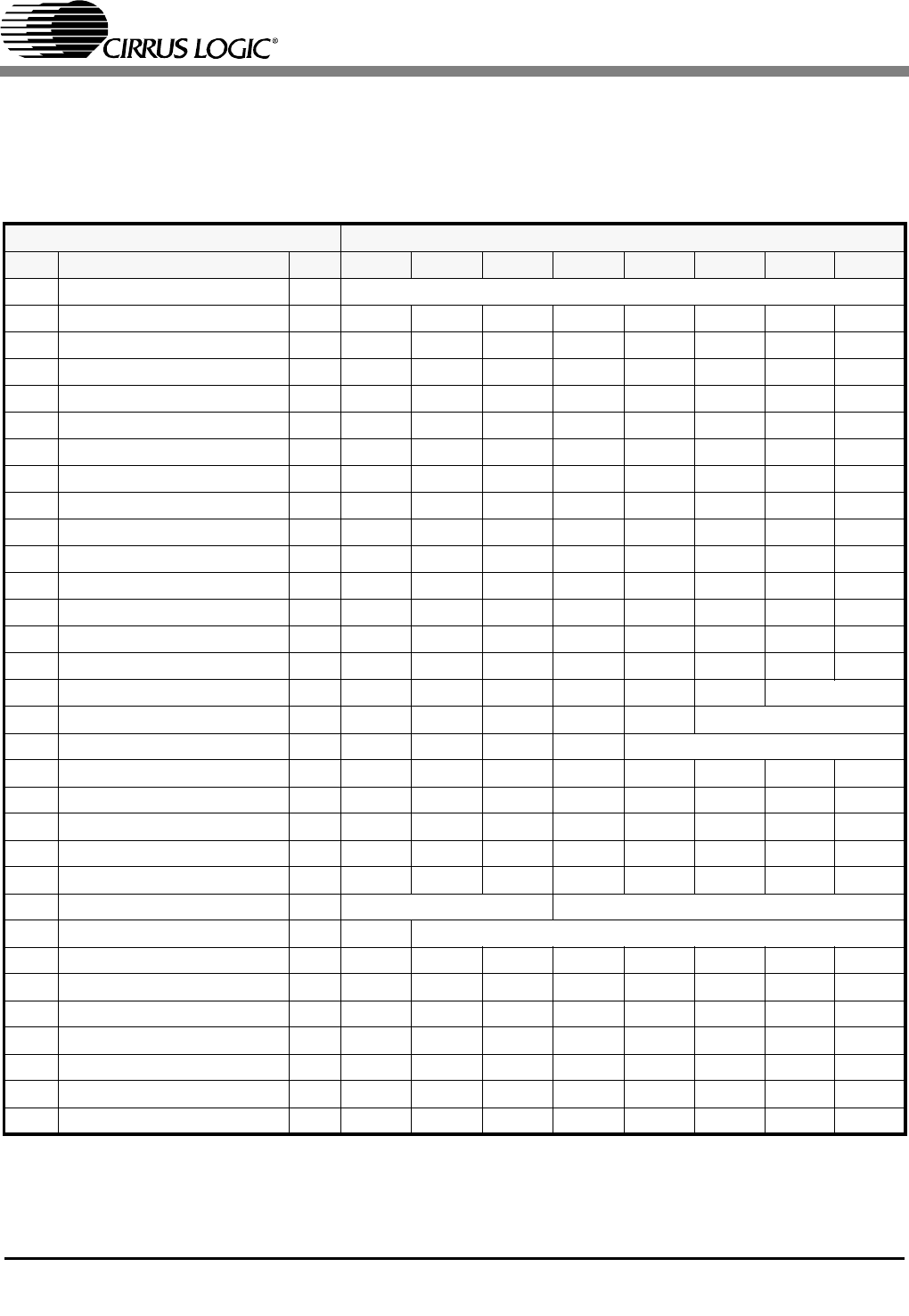

13.4 Register Set

The register set available during host mode opera-

tions are presented in Table 10. While the upper

three bits of the parallel address are don’t cares on

the CS61880, they should be set to zero for proper

operation.

Table 10. Host Mode Register Set

REGISTERS BITS

ADDR NAME TYPE 7 6 5 4 3 2 1 0

00h

Revision/IDCODE R IDCODE Refer to Device ID Register (IDR) on page 47

01h

Analog Loopback R/W ALBK 7 ALBK 6 ALBK 5 ALBK 4 ALBK 3 ALBK 2 ALBK 1 ALBK 0

02h

Remote Loopback R/W RLBK 7 RLBK 6 RLBK 5 RLBK 4 RLBK 3 RLBK 2 RLBK 1 RLBK 0

03h

TAOS Enable R/W TAOE 7 TAOE 6 TAOE 5 TAOE 4 TAOE 3 TAOE 2 TAOE 1 TAOE 0

04h

LOS Status R LOSS 7 LOSS 6 LOSS 5 LOSS 4 LOSS 3 LOSS 2 LOSS 1 LOSS 0

05h

DFM Status R DFMS 7 DFMS 6 DFMS 5 DFMS 4 DFMS 3 DFMS 2 DFMS 1 DFMS 0

06h

LOS Interrupt Enable R/W LOSE 7 LOSE 6 LOSE 5 LOSE 4 LOSE 3 LOSE 2 LOSE 1 LOSE 0

07h

DFM Interrupt Enable R/W DFME 7 DFME 6 DFME 5 DFME 4 DFME 3 DFME 2 DFME 1 DFME 0

08h

LOS Interrupt Status R LOSI 7 LOSI 6 LOSI 5 LOSI 4 LOSI 3 LOSI 2 LOSI 1 LOSI 0

09h

DFM Interrupt Status R DFMI 7 DFMI 6 DFMI 5 DFMI 4 DFMI 3 DFMI 2 DFMI 1 DFMI 0

0Ah

Software Reset R/W SRES 7 SRES 6 SRES 5 SRES 4 SRES 3 SRES 2 SRES 1 SRES 0

0Bh

Performance Monitor R/W RSVD RSVD RSVD RSVD A3 A2 A1 A0

0Ch

Digital Loopback R/W DLBK 7 DLBK 6 DLBK 5 DLBK 4 DLBK 3 DLBK 2 DLBK 1 DLBK 0

0Dh

LOS/AIS Mode Enable R/W LAME 7 LAME 6 LAME 5 LAME 4 LAME 3 LAME 2 LAME 1 LAME 0

0Eh

Automatic TAOS R/W ATAO 7 ATAO 6 ATAO 5 ATAO 4 ATAO 3 ATAO 2 ATAO 1 ATAO 0

0Fh

Global Control R/W AI Raisen RSVD Coden FIFO JACF JASEL [1:0]

10h

Line Length Channel ID R/W RSVD RSVD RSVD RSVD RSVD Channel ID

11h

Line Length Data R/W RSVD RSVD RSVD IN_EX LEN[3:0]

12h

Output Disable R/W OENB 7 OENB 6 OENB 5 OENB 4 OENB 3 OENB 2 OENB 1 OENB 0

13h

AIS Status R AISS 7 AISS 6 AISS 5 AISS 4 AISS 3 AISS 2 AISS 1 AISS 0

14h

AIS Interrupt Enable R/W AISE 7 AISE 6 AISE 5 AISE 4 AISE 3 AISE 2 AISE 1 AISE 0

15h

AIS Interrupt Status R AISI 7 AISI 6 AISI 5 AISI 4 AISI 3 AISI 2 AISI 1 AISI 0

16h

AWG Broadcast R/W AWGB 7 AWGB 6 AWGB 5 AWGB 4 AWGB 3 AWGB 2 AWGB 1 AWGB 0

17h

AWG Phase Address R/W Channel Address [2:0] Phase Address [4:0]

18h

AWG Phase Data R/W RSVD Sample Data[6:0]

19h

AWG Enable R/W AWGN 7 AWGN 6 AWGN 5 AWGN 4 AWGN 3 AWGN 2 AWGN 1 AWGN 0

1Ah

RESERVED R/W RSVD 7 RSVD 6 RSVD 5 RSVD 4 RSVD 3 RSVD 2 RSVD 1 RSVD 0

1Bh

RESERVED R RSVD 7 RSVD 6 RSVD 5 RSVD 4 RSVD 3 RSVD 2 RSVD 1 RSVD 0

1Ch

RESERVED R/W RSVD 7 RSVD 6 RSVD 5 RSVD 4 RSVD 3 RSVD 2 RSVD 1 RSVD 0

1Dh

RESERVED R RSVD 7 RSVD 6 RSVD 5 RSVD 4 RSVD 3 RSVD 2 RSVD 1 RSVD 0

1Eh

BITS Clock Enable R/W BITS 7 BITS 6 BITS 5 BITS 4 BITS 3 BITS 2 BITS 1 BITS 0

1Fh

RESERVED R/W RSVD 7 RSVD 6 RSVD 5 RSVD 4 RSVD 3 RSVD 2 RSVD 1 RSVD 0