Instruction Manual

Table Of Contents

- Features & Description

- General Description

- Table of Contents

- List of Figures

- List of Tables

- 1. Characteristics and Specifications

- 2. Overview

- 3. Theory of Operation

- 3.1 Converter Operation

- 3.2 Clock

- 3.3 Voltage Reference

- 3.4 Analog Input

- 3.5 Output Coding Format

- 3.6 Typical Connection Diagrams

- 3.7 AIN & VREF Sampling Structures

- 3.8 Converter Performance

- 3.9 Digital Filter Characteristics

- 3.10 Serial Port

- 3.11 Power Supplies & Grounding

- 3.12 Using the CS5581 in Multiplexing Applications

- 3.13 Synchronizing Multiple Converters

- 4. Pin Descriptions

- 5. Package Dimensions

- 6. Ordering Information

- 7. Environmental, Manufacturing, & Handling Information

- 8. Revision History

CS5581

DS796PP1 9

3/25/08

14:34

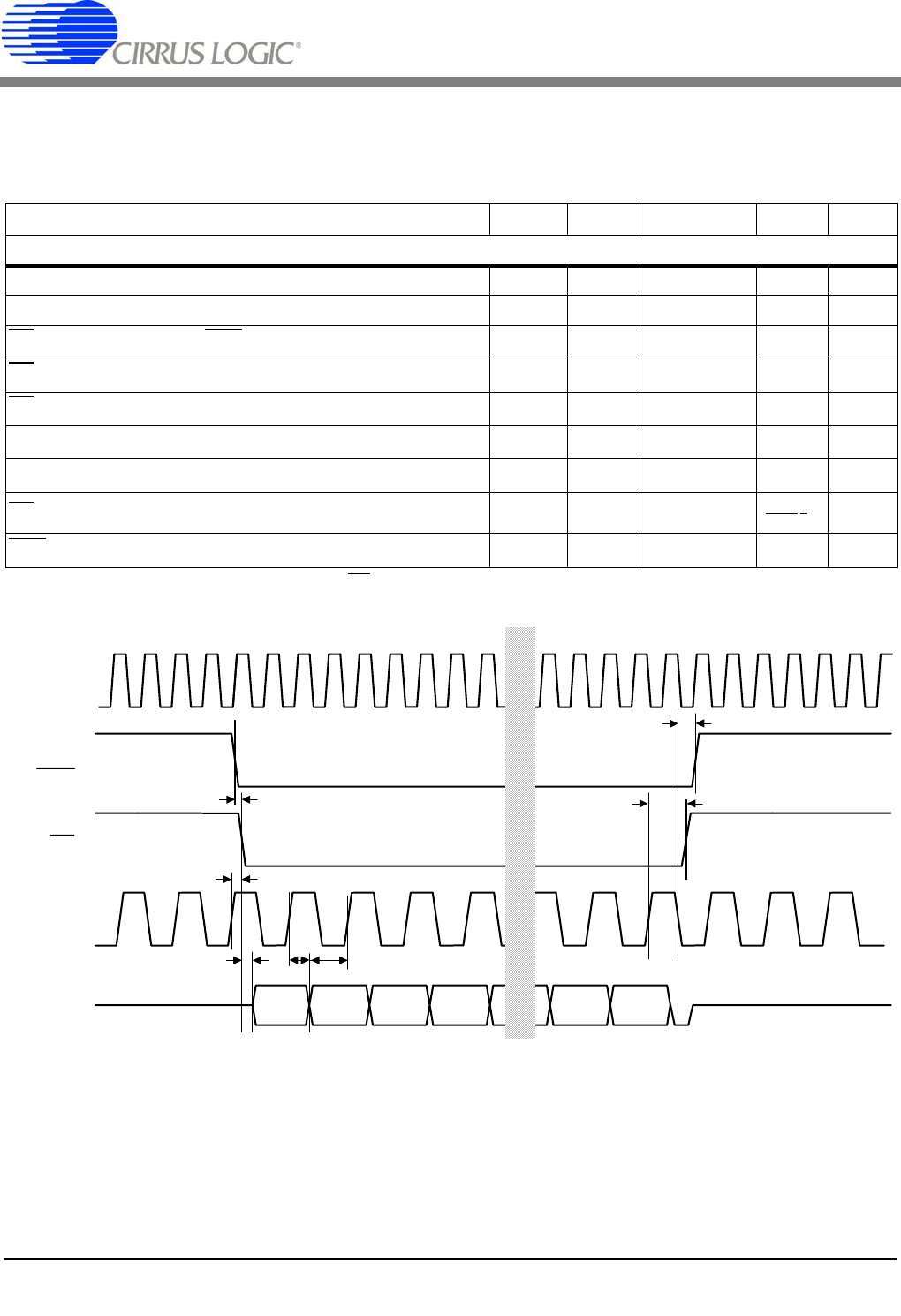

SWITCHING CHARACTERISTICS (CONTINUED)

T

A

= -40 to +85 °C; V1+ = V2+ = +2.5 V, ±5%; V1- = V2- = -2.5 V, ±5%;

VL - VLR = 3.3 V, ±5%, 2.5 V, ±5%, or 1.8 V, ±5%

Input levels: Logic 0 = 0V = Low; Logic 1 = VD+ = High; CL = 15 pF.

15. SDO will be high impedance when CS is high. In some systems SDO may require a pull-down resistor.

Parameter Symbol Min Typ Max Unit

Serial Port Timing in SEC Mode (SMODE = VLR)

SCLK(in) Pulse Width (High)

-

30 - - ns

SCLK(in) Pulse Width (Low)

-

30 - - ns

CS

hold time (high) after RDY falling t

15

10 - - ns

CS

hold time (high) after SCLK rising t

16

10 - - ns

CS

low to SDO out of Hi-Z (Note 15) t

17

-10-ns

Data hold time after SCLK rising t

18

-10-ns

Data setup time before SCLK rising t

19

10 - - ns

CS

hold time (low) after SCLK rising

t

20

10 - ns

RDY

rising after SCLK falling t

21

-10-ns

1

SCLK

10

MCLK

SCLK(i)

SDO

CS

RDY

LSBMSB

t

19

t

18

t

20

t

17

t

16

t

15

t

21

Figure 3. SEC Mode - Continuous SCLK Read Timing (Not to Scale)