Manual

Table Of Contents

- Features & Description

- Table of Contents

- List of Figures

- List of Tables

- 1. Characteristics and Specifications

- Analog Characteristics

- Analog Characteristics (Continued)

- Switching Characteristics

- Switching Characteristics (Continued)

- Switching Characteristics (Continued)

- Switching Characteristics (Continued)

- Digital Characteristics

- Digital Filter Characteristics

- Guaranteed Logic Levels

- Recommended Operating Conditions

- Absolute Maximum Ratings

- 2. Overview

- 3. Theory of Operation

- 3.1 Converter Operation

- 3.2 Clock

- 3.3 Voltage Reference

- 3.4 Analog Input

- 3.5 Output Coding Format

- 3.6 Typical Connection Diagrams

- 3.7 AIN & VREF Sampling Structures

- 3.8 Converter Performance

- 3.9 Digital Filter Characteristics

- 3.10 Serial Port

- 3.11 Power Supplies & Grounding

- 3.12 Using the CS5560 in Multiplexing Applications

- 3.13 Synchronizing Multiple Converters

- 4. Pin Descriptions

- 5. Package Dimensions

- 6. Ordering Information

- 7. Environmental, Manufacturing, & Handling Information

- 8. Revision History

CS5560

18 DS713PP2

5/4/09

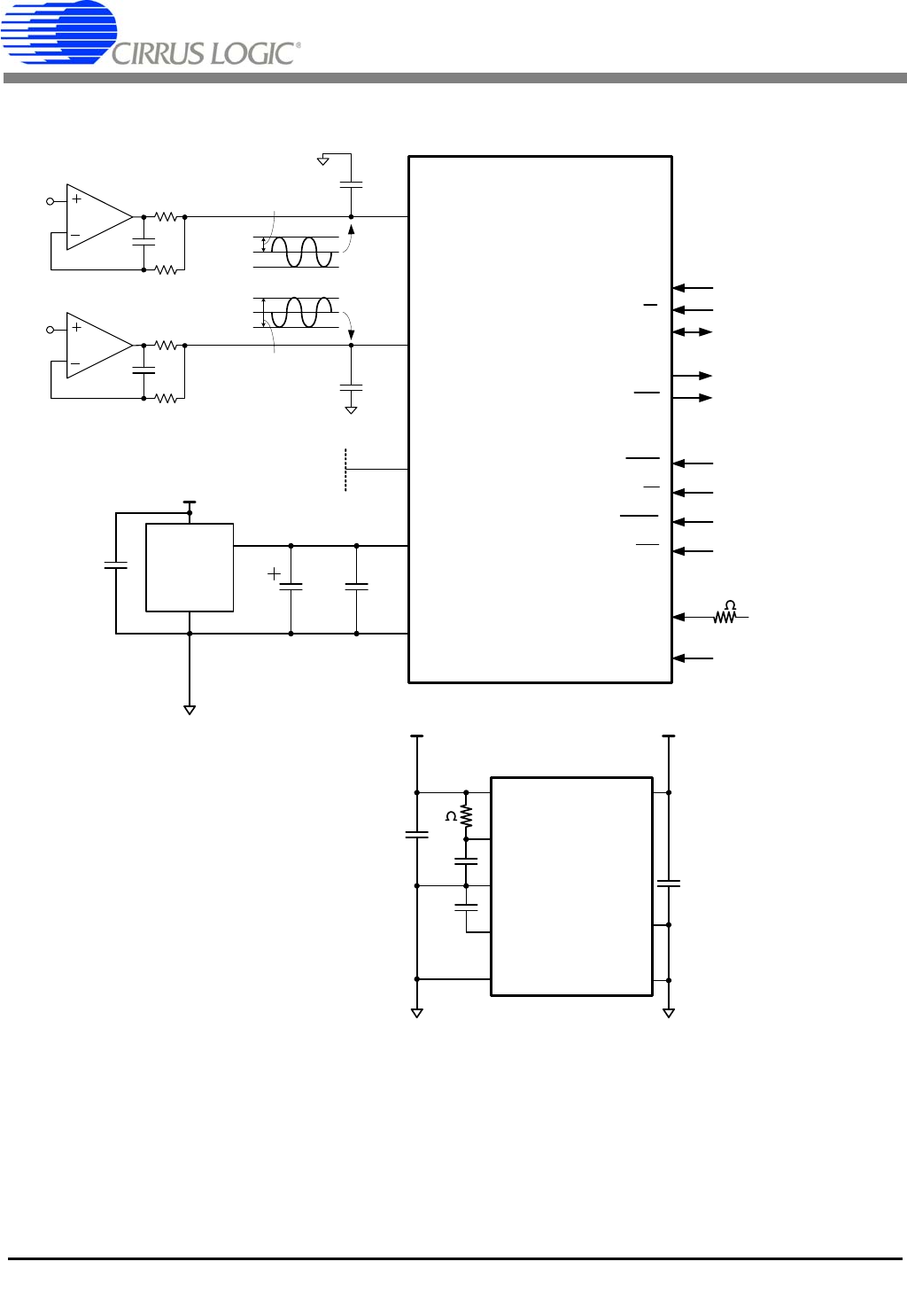

The following figure depicts the CS5560 device powered from a single 5V analog supply.

Figure 7. CS5560 Configured Using a Single 5V Analog Supply

AIN-

AIN+

SMODE

CS

4

SCLK

4

SDO

RDY

CONV

BP/UP

MCLK

SLEEP

RST

TST

VREF-

VREF+

+4.096

Voltage

Reference

(NOTE 1)

+5 V

BUFEN

1. See Section 3.3 Voltage Reference for information on

required voltage reference performance criteria.

2. Locate capacitors so as to minimize loop length.

3. V1-, V2-, and VLR should be connected to the same

ground plane under the chip.

4. SCLK and SDO may require pull-down resistors in

some applications.

NOTES

0.1 µF

(V-) Buffers Off

(V+) Buffers On

0.1 µF10 µF

V1+

V2+

V1-

V2-

VL

VLR

DCR

+5 V

+3.3 V to 1.8 V

0.1 µF

0.1 µF

X7R

0.1 µF

10

CS5560

49.9

47pF

4.99k

4700pF

C0G

49.9

47pF

4.99k

4700pF

C0G

+0.452 V

4.548 V

2.5 V

+4.548 V

+0.452 V

2.5 V

2.048 V

4.096 V

VLR2

50