User Manual

Table Of Contents

- 1. Pin Description

- 2. Characteristics and Specifications

- Recommended Operating Conditions

- Absolute Maximum Ratings

- DAC Analog Characteristics

- Power and Thermal Characteristics

- Combined Interpolation & On-Chip Analog Filter Response

- Combined Interpolation & On-Chip Analog Filter Response

- DSD Combined Digital & On-Chip Analog Filter Response

- Digital Characteristics

- Switching Characteristics - PCM

- Switching Characteristics - DSD

- Switching Characteristics - Control Port - I·C Format

- Switching Characteristics - Control Port - SPI Format

- 3. Typical Connection Diagram

- 4. Applications

- 4.1 Master Clock

- 4.2 Mode Select

- 4.3 Digital Interface Formats

- Figure 8. Format 0 - Left-Justified up to 24-bit Data

- Figure 9. Format 1 - I·S up to 24-bit Data

- Figure 10. Format 2 - Right-Justified 16-bit Data

- Figure 11. Format 3 - Right-Justified 24-bit Data

- Figure 12. Format 4 - Right-Justified 20-bit Data

- Figure 13. Format 5 - Right-Justified 18-bit Data

- 4.3.1 OLM #1

- 4.3.2 OLM #2

- 4.4 Oversampling Modes

- 4.5 Interpolation Filter

- 4.6 De-Emphasis

- 4.7 ATAPI Specification

- 4.8 Direct Stream Digital (DSD) Mode

- 4.9 Grounding and Power Supply Arrangements

- 4.10 Analog Output and Filtering

- 4.11 The MUTEC Outputs

- 4.12 Recommended Power-Up Sequence

- 4.13 Recommended Procedure for Switching Operational Modes

- 4.14 Control Port Interface

- 4.15 Memory Address Pointer (MAP)

- 5. Register Quick Reference

- 6. Register Description

- 6.1 Chip Revision (Address 01h)

- 6.2 Mode Control 1 (Address 02h)

- 6.3 PCM Control (Address 03h)

- 6.4 DSD Control (Address 04h)

- 6.5 Filter Control (Address 05h)

- 6.6 Invert Control (Address 06h)

- 6.7 Group Control (Address 07h)

- 6.8 Ramp and Mute (Address 08h)

- 6.9 Mute Control (Address 09h)

- 6.10 Mixing Control (Address 0Ah, 0Dh, 10h, 13h)

- 6.11 Volume Control (Address 0Bh, 0Ch, 0Eh, 0Fh, 11h, 12h)

- 6.12 PCM Clock Mode (Address 16h)

- 7. Filter Response Plots

- Figure 24. Single-Speed (fast) Stopband Rejection

- Figure 25. Single-Speed (fast) Transition Band

- Figure 26. Single-Speed (fast) Transition Band (detail)

- Figure 27. Single-Speed (fast) Passband Ripple

- Figure 28. Single-Speed (slow) Stopband Rejection

- Figure 29. Single-Speed (slow) Transition Band

- Figure 30. Single-Speed (slow) Transition Band (detail)

- Figure 31. Single-Speed (slow) Passband Ripple

- Figure 32. Double-Speed (fast) Stopband Rejection

- Figure 33. Double-Speed (fast) Transition Band

- Figure 34. Double-Speed (fast) Transition Band (detail)

- Figure 35. Double-Speed (fast) Passband Ripple

- Figure 36. Double-Speed (slow) Stopband Rejection

- Figure 37. Double-Speed (slow) Transition Band

- Figure 38. Double-Speed (slow) Transition Band (detail)

- Figure 39. Double-Speed (slow) Passband Ripple

- Figure 40. Quad-Speed (fast) Stopband Rejection

- Figure 41. Quad-Speed (fast) Transition Band

- Figure 42. Quad-Speed (fast) Transition Band (detail)

- Figure 43. Quad-Speed (fast) Passband Ripple

- Figure 44. Quad-Speed (slow) Stopband Rejection

- Figure 45. Quad-Speed (slow) Transition Band

- Figure 46. Quad-Speed (slow) Transition Band (detail)

- Figure 47. Quad-Speed (slow) Passband Ripple

- 8. References

- 9. Parameter Definitions

- 10. Package Dimensions

- 11. Ordering Information

- 12. Revision History

DS619F1 21

CS4364

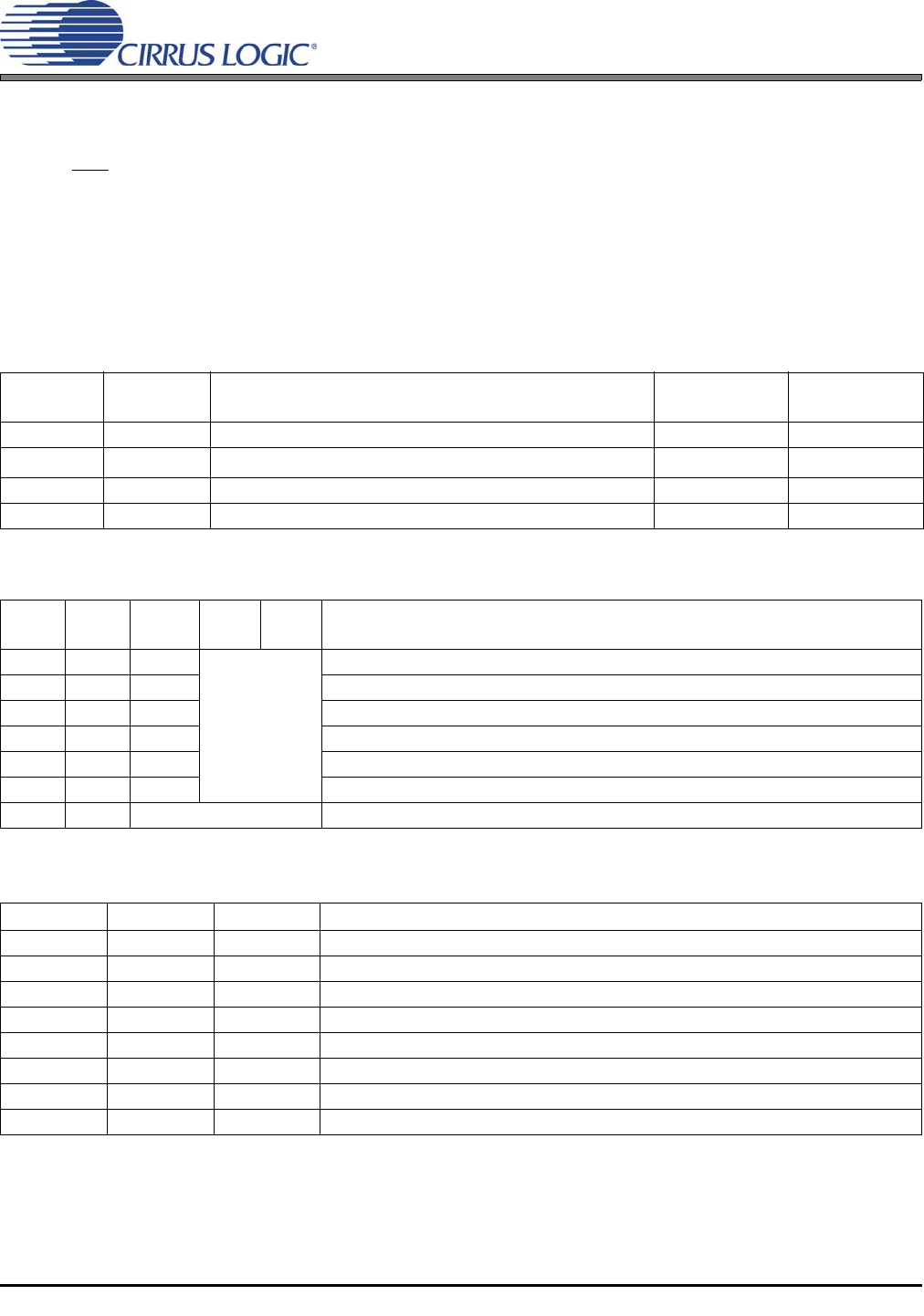

4.2 Mode Select

In Hardware Mode, operation is determined by the Mode Select pins. The states of these pins are continu-

ally scanned for any changes; however, the mode should only be changed while the device is in reset

(RST

pin low) to ensure proper switching from one mode to another. These pins require connection to sup-

ply or ground as outlined in Figure 7. For M0, M1, and M2, supply is VLC. For M3 and M4, supply is VLS.

Tables 4 - 6 show the decode of these pins.

In Software Mode, the operational mode and data format are set in the FM and DIF registers. See “PCM

Control (Address 03h)” on page 34.

M1

(DIF1)

M0

(DIF0)

DESCRIPTION FORMAT FIGURE

00

Left Justified, up to 24-bit data

0 8

01

I

2

S, up to 24-bit data

1 9

10

Right Justified, 16-bit Data

2 10

11

Right Justified, 24-bit Data

3 11

Table 4. PCM Digital Interface Format, Hardware Mode Options

M4 M3 M2

(DEM)

M1 M0 DESCRIPTION

000

Table 4

Single-Speed without De-Emphasis (4 kHz to 50 kHz sample rates)

001

Single-Speed with 44.1 kHz De-Emphasis; see Figure 16

010

Double-Speed (50 kHz to 100 kHz sample rates)

011

Quad-Speed (100 kHz to 200 kHz sample rates)

100

Auto Speed-Mode Detect (32 kHz to 200 kHz sample rates)

101

Auto Speed-Mode Detect with 44.1 kHz De-Emphasis; see Figure 16

11 Table 6

DSD Processor Mode

Table 5. Mode Selection, Hardware Mode Options

M2 M1 M0 DESCRIPTION

000

64x oversampled DSD data with a 4x MCLK to DSD data rate

001

64x oversampled DSD data with a 6x MCLK to DSD data rate

010

64x oversampled DSD data with a 8x MCLK to DSD data rate

011

64x oversampled DSD data with a 12x MCLK to DSD data rate

100

128x oversampled DSD data with a 2x MCLK to DSD data rate

101

128x oversampled DSD data with a 3x MCLK to DSD data rate

110

128x oversampled DSD data with a 4x MCLK to DSD data rate

111

128x oversampled DSD data with a 6x MCLK to DSD data rate

Table 6. Direct Stream Digital (DSD), Hardware Mode Options