User Manual

Table Of Contents

- 1. Pin Description

- 2. Characteristics and Specifications

- Recommended Operating Conditions

- Absolute Maximum Ratings

- DAC Analog Characteristics

- Power and Thermal Characteristics

- Combined Interpolation & On-Chip Analog Filter Response

- Combined Interpolation & On-Chip Analog Filter Response

- DSD Combined Digital & On-Chip Analog Filter Response

- Digital Characteristics

- Switching Characteristics - PCM

- Switching Characteristics - DSD

- Switching Characteristics - Control Port - I·C Format

- Switching Characteristics - Control Port - SPI Format

- 3. Typical Connection Diagram

- 4. Applications

- 4.1 Master Clock

- 4.2 Mode Select

- 4.3 Digital Interface Formats

- Figure 8. Format 0 - Left-Justified up to 24-bit Data

- Figure 9. Format 1 - I·S up to 24-bit Data

- Figure 10. Format 2 - Right-Justified 16-bit Data

- Figure 11. Format 3 - Right-Justified 24-bit Data

- Figure 12. Format 4 - Right-Justified 20-bit Data

- Figure 13. Format 5 - Right-Justified 18-bit Data

- 4.3.1 OLM #1

- 4.3.2 OLM #2

- 4.4 Oversampling Modes

- 4.5 Interpolation Filter

- 4.6 De-Emphasis

- 4.7 ATAPI Specification

- 4.8 Direct Stream Digital (DSD) Mode

- 4.9 Grounding and Power Supply Arrangements

- 4.10 Analog Output and Filtering

- 4.11 The MUTEC Outputs

- 4.12 Recommended Power-Up Sequence

- 4.13 Recommended Procedure for Switching Operational Modes

- 4.14 Control Port Interface

- 4.15 Memory Address Pointer (MAP)

- 5. Register Quick Reference

- 6. Register Description

- 6.1 Chip Revision (Address 01h)

- 6.2 Mode Control 1 (Address 02h)

- 6.3 PCM Control (Address 03h)

- 6.4 DSD Control (Address 04h)

- 6.5 Filter Control (Address 05h)

- 6.6 Invert Control (Address 06h)

- 6.7 Group Control (Address 07h)

- 6.8 Ramp and Mute (Address 08h)

- 6.9 Mute Control (Address 09h)

- 6.10 Mixing Control (Address 0Ah, 0Dh, 10h, 13h)

- 6.11 Volume Control (Address 0Bh, 0Ch, 0Eh, 0Fh, 11h, 12h)

- 6.12 PCM Clock Mode (Address 16h)

- 7. Filter Response Plots

- Figure 24. Single-Speed (fast) Stopband Rejection

- Figure 25. Single-Speed (fast) Transition Band

- Figure 26. Single-Speed (fast) Transition Band (detail)

- Figure 27. Single-Speed (fast) Passband Ripple

- Figure 28. Single-Speed (slow) Stopband Rejection

- Figure 29. Single-Speed (slow) Transition Band

- Figure 30. Single-Speed (slow) Transition Band (detail)

- Figure 31. Single-Speed (slow) Passband Ripple

- Figure 32. Double-Speed (fast) Stopband Rejection

- Figure 33. Double-Speed (fast) Transition Band

- Figure 34. Double-Speed (fast) Transition Band (detail)

- Figure 35. Double-Speed (fast) Passband Ripple

- Figure 36. Double-Speed (slow) Stopband Rejection

- Figure 37. Double-Speed (slow) Transition Band

- Figure 38. Double-Speed (slow) Transition Band (detail)

- Figure 39. Double-Speed (slow) Passband Ripple

- Figure 40. Quad-Speed (fast) Stopband Rejection

- Figure 41. Quad-Speed (fast) Transition Band

- Figure 42. Quad-Speed (fast) Transition Band (detail)

- Figure 43. Quad-Speed (fast) Passband Ripple

- Figure 44. Quad-Speed (slow) Stopband Rejection

- Figure 45. Quad-Speed (slow) Transition Band

- Figure 46. Quad-Speed (slow) Transition Band (detail)

- Figure 47. Quad-Speed (slow) Passband Ripple

- 8. References

- 9. Parameter Definitions

- 10. Package Dimensions

- 11. Ordering Information

- 12. Revision History

14 DS619F1

CS4364

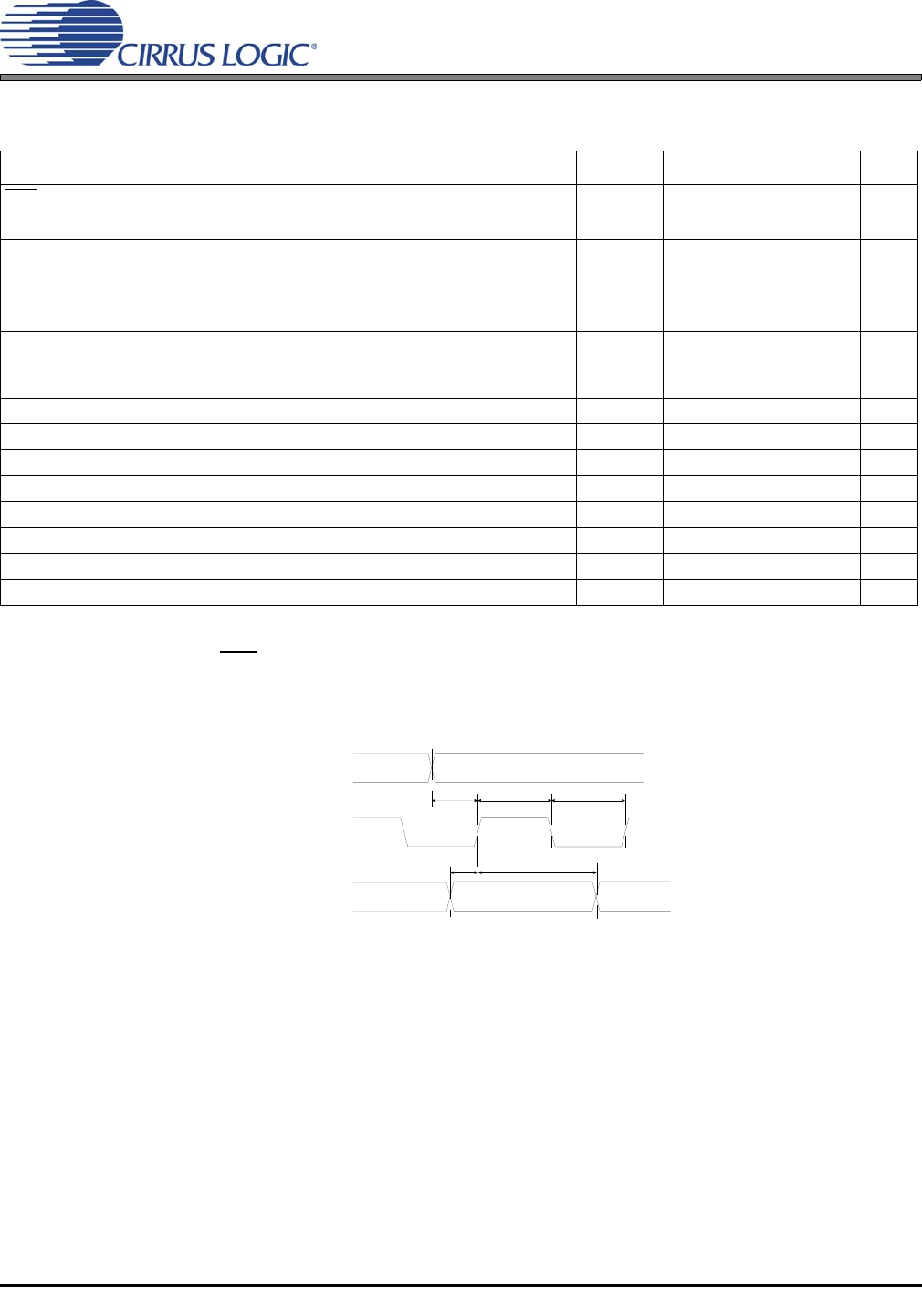

SWITCHING CHARACTERISTICS - PCM

(Inputs: Logic 0 = GND, Logic 1 = VLS, C

L

= 30 pF)

Notes:

14. After powering up, RST

should be held low until after the power supplies and clocks are settled.

15. See Tables 1 - 3 for suggested MCLK frequencies.

Parameters Symbol Min Max Units

RST pin Low Pulse Width (Note 14)

1-ms

MCLK Frequency 1.024 55.2 MHz

MCLK Duty Cycle (Note 15) 45 55 %

Input Sample Rate - LRCK (Manual selection) Single-Speed Mode

Double-Speed Mode

Quad-Speed Mode

F

s

F

s

F

s

4

50

100

54

108

216

kHz

kHz

kHz

Input Sample Rate - LRCK (Auto detect) Single-Speed Mode

Double-Speed Mode

Quad-Speed Mode

Fs

Fs

Fs

4

84

170

54

108

216

kHz

kHz

kHz

LRCK Duty Cycle 45 55 %

SCLK Duty Cycle 45 55 %

SCLK High Time t

sckh

8-ns

SCLK Low Time t

sckl

8-ns

LRCK Edge to SCLK Rising Edge t

lcks

5-ns

SCLK Rising Edge to LRCK Falling Edge t

lckd

5-ns

SDIN Setup Time Before SCLK Rising Edge t

ds

3-ns

SDIN Hold Time After SCLK Rising Edge t

dh

5-ns

SDINx

t

ds

SCLK

LRCK

MSB

t

dh

t

sckh

t

sckl

t

lcks

MSB-1

Figure 1. Serial Audio Interface Timing