User Manual

Table Of Contents

- 1. Pin Descriptions

- 2. Typical Connection Diagram

- 3. Characteristic and Specifications

- Recommended Operating Conditions

- Absolute Maximum Ratings

- Analog Input Characteristics

- ADC Digital Filter Characteristics

- Analog Output Characteristics

- Analog Passthrough Characteristics

- PWM Output Characteristics

- Headphone Output Power Characteristics

- Line Output Voltage Level Characteristics

- Combined DAC Interpolation and onChip Analog FIlter Response

- Switching Specifications - Serial Port

- Switching Specifications - I²C Control Port

- DC Electrical Characteristics

- Digital Interface Specifications and Characteristics

- Power Consumption

- 4. Applications

- 4.1 Overview

- 4.2 Analog Inputs

- 4.3 Analog Outputs

- 4.4 Analog In to Analog Out Passthrough

- 4.5 PWM Outputs

- 4.6 Serial Port Clocking

- 4.7 Digital Interface Formats

- 4.8 Initialization

- 4.9 Recommended Power-up Sequence

- 4.10 Recommended Power-Down Sequence

- 4.11 Required Initialization Settings

- 4.12 Control Port Operation

- 5. Register Quick Reference

- 6. Register Description

- 6.1 Chip I.D. and Revision Register (Address 01h) (Read Only)

- 6.2 Power Control 1 (Address 02h)

- 6.3 Power Control 2 (Address 03h)

- 6.4 Power Control 3 (Address 04h)

- 6.5 Clocking Control (Address 05h)

- 6.6 Interface Control 1 (Address 06h)

- 6.7 Interface Control 2 (Address 07h)

- 6.8 Input x Select: ADCA and PGAA (Address 08h), ADCB and PGAB (Address 09h)

- 6.9 Analog and HPF Control (Address 0Ah)

- 6.10 ADC HPF Corner Frequency (Address 0Bh)

- 6.11 Misc. ADC Control (Address 0Ch)

- 6.12 Playback Control 1 (Address 0Dh)

- 6.13 Miscellaneous Controls (Address 0Eh)

- 6.14 Playback Control 2 (Address 0Fh)

- 6.15 MICx Amp Control:MIC A (Address 10h) and MIC B (Address 11h)

- 6.16 PGAx Vol. and ALCx Transition Ctl.: ALC, PGA A (Address 12h) and ALC, PGA B (Address 13h)

- 6.17 Passthrough x Volume: PASSAVOL (Address 14h) and PASSBVOL (Address 15h)

- 6.18 ADCx Volume Control: ADCAVOL (Address 16h) and ADCBVOL (Address 17h)

- 6.19 ADCx Mixer Volume: ADCA (Address 18h) and ADCB (Address 19h)

- 6.20 PCMx Mixer Volume: PCMA (Address 1Ah) and PCMB (Address 1Bh)

- 6.21 Beep Frequency and On Time (Address 1Ch)

- 6.22 Beep Volume and Off Time (Address 1Dh)

- 6.23 Beep and Tone Configuration (Address 1Eh)

- 6.24 Tone Control (Address 1Fh)

- 6.25 Master Volume Control: MSTA (Address 20h) and MSTB (Address 21h)

- 6.26 Headphone Volume Control: HPA (Address 22h) and HPB (Address 23h)

- 6.27 Speaker Volume Control: SPKA (Address 24h) and SPKB (Address 25h)

- 6.28 ADC and PCM Channel Mixer (Address 26h)

- 6.29 Limiter Control 1, Min/Max Thresholds (Address 27h)

- 6.30 Limiter Control 2, Release Rate (Address 28h)

- 6.31 Limiter Attack Rate (Address 29h)

- 6.32 ALC Enable and Attack Rate (Address 2Ah)

- 6.33 ALC Release Rate (Address 2Bh)

- 6.34 ALC Threshold (Address 2Ch)

- 6.35 Noise Gate Control (Address 2Dh)

- 6.36 Status (Address 2Eh) (Read Only)

- 6.37 Battery Compensation (Address 2Fh)

- 6.38 VP Battery Level (Address 30h) (Read Only)

- 6.39 Speaker Status (Address 31h) (Read Only)

- 6.40 Charge Pump Frequency (Address 34h)

- 7. Analog Performance Plots

- 8. Example System Clock Frequencies

- 9. PCB Layout Considerations

- 10. ADC and DAC Digital Filters

- 11. Parameter Definitions

- 12. Package Dimensions

- 13. Ordering Information

- 14. References

- 15. Revision History

66 DS680F2

CS42L52

3/1/13

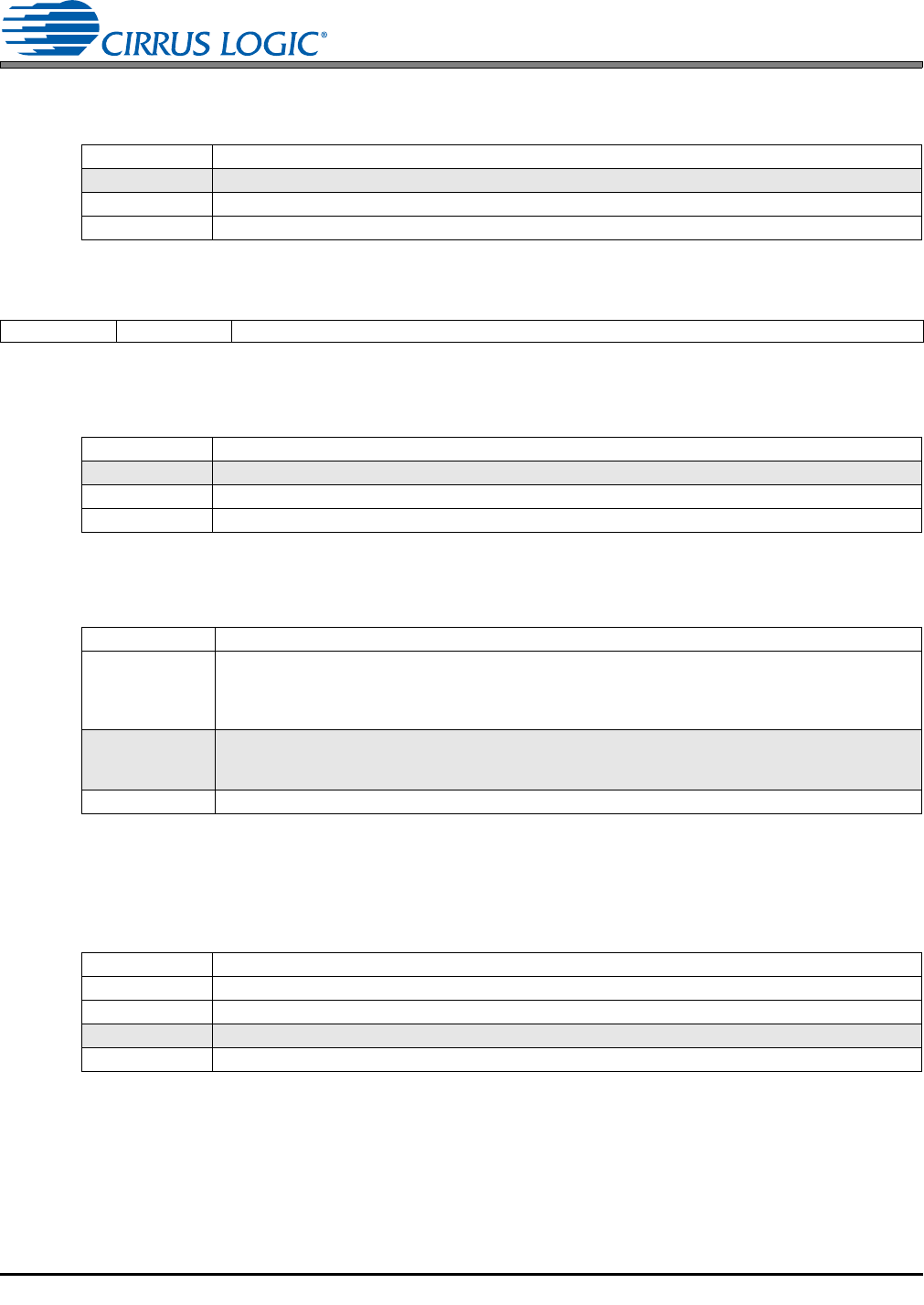

6.29.4 Limiter Zero Cross Disable

Configures an override of the digital zero-cross setting.

6.30 Limiter Control 2, Release Rate (Address 28h)

6.30.1 Peak Detect and Limiter

Configures the peak-detect and limiter circuitry.

6.30.2 Peak Signal Limit All Channels

Sets how channels are attenuated when the limiter is enabled.

6.30.3 Limiter Release Rate

Sets the rate at which the limiter releases the digital attenuation from levels below the CUSH[2:0] thresh-

old (“Limiter Cushion Threshold” on page 65) and returns the analog output level to the MSTxVOL[7:0]

(“Master Volume Control” on page 63) setting.

Note: The limiter release rate is user-selectable but is also a function of the sampling frequency, Fs,

and the DIGSFT (“Digital Soft Ramp” on page 53) and DIGZC (“Digital Zero Cross” on page 53) setting.

LIMZCDIS Limiter Zero Cross Disable

0 OFF; Limiter Attack Rate is dictated by the DIGZC (“Digital Zero Cross” on page 53) setting

1 ON; Limiter volume changes take effect in one step, regardless of the DIGZC setting.

Application: “Limiter” on page 30

76543210

LIMIT LIMIT_ALL LIMRRATE5 LIMRRATE4 LIMRRATE3 LIMRRATE2 LIMRRATE1 LIMRRATE0

LIMIT Limiter Status

0 Disabled

1 Enabled

Application: “Limiter” on page 30

LIMIT_ALL Limiter action:

0

Apply the necessary attenuation on a specific channel only when the signal amplitude on

that specific chan-

nel rises above LMAX.

Remove attenuation on a specific channel only when the signal amplitude on

that specific channel falls below

CUSH.

1

Apply the necessary attenuation on BOTH channels when the signal amplitude on any ONE channel rises

above LMAX.

Remove attenuation on BOTH channels only when the signal amplitude on BOTH channels fall below CUSH.

Application: “Limiter” on page 30

LIMRRATE[5:0] Release Time

00 0000 Fastest Release

··· ···

11 1111 Slowest Release

Application: “Limiter” on page 30