Instruction Manual

38 DS657F3

CS4265

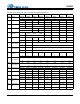

6.3.3 De-Emphasis Control (Bit 1)

Function:

The standard 50/15 s digital de-emphasis filter response, Figure 17, may be implemented for a sample

rate of 44.1 kHz when the DeEmph bit is configured as shown in Table 8. NOTE: De-emphasis is available

only in Single-Speed Mode.

6.4 ADC Control - Address 04h

6.4.1 Functional Mode (Bits 7:6)

Function:

Selects the required range of sample rates.

6.4.2 ADC Digital Interface Format (Bit 4)

Function:

The required relationship between LRCK, SCLK and SDOUT is defined by the ADC Digital Interface For-

mat bit. The options are detailed in Table 10 and may be seen in Figure 5 and Figure 6.

DeEmph Description

0 Disabled (default)

1 44.1 kHz de-emphasis

Table 8. De-Emphasis Control

76543210

FM1 FM0 Reserved ADC_DIF Reserved MuteADC HPFFreeze M/S

FM1 FM0 Mode

0 0 Single-Speed Mode: 4 to 50 kHz sample rates

0 1 Double-Speed Mode: 50 to 100 kHz sample rates

1 0 Quad-Speed Mode: 100 to 200 kHz sample rates

11Reserved

Table 9. Functional Mode Selection

Gain

dB

-10dB

0dB

Frequency

T2 = 15 µs

T1=50 µs

F1 F2

3.183 kHz 10.61 kHz

Figure 17. De-Emphasis Curve