User guide

Table Of Contents

- 1. Characteristics and Specifications

- Specified Operating Conditions

- Absolute Maximum Ratings

- Analog Input Characteristics

- A/D Digital Filter Characteristics

- Analog Output Characteristics

- D/A Digital Filter Characteristics

- Switching Characteristics

- Switching Characteristics - Control Port - I²C™ Format

- Switching Characteristics - Control Port - SPI™ Format

- DC Electrical Characteristics

- Digital Interface Characteristics

- 2. Pin Descriptions

- 3. Typical Connection Diagram

- 4. Applications

- 4.1 Overview

- 4.2 Analog Inputs

- 4.3 Analog Outputs

- 4.4 S/PDIF Receiver

- 4.5 Clock Generation

- 4.6 Digital Interfaces

- 4.7 Control Port Description and Timing

- 4.8 Interrupts

- 4.9 Reset and Power-Up

- 4.10 Power Supply, Grounding, and PCB Layout

- 5. Register Quick Reference

- 6. Register Description

- Table 5. DAC De-Emphasis

- Table 6. Receiver De-Emphasis

- Table 7. Digital Interface Formats

- Table 8. ADC One-Line Mode

- Table 9. DAC One-Line Mode

- Table 10. RMCK Divider Settings

- Table 11. OMCK Frequency Settings

- Table 12. Master Clock Source Select

- Table 13. AES Format Detection

- Table 14. Receiver Clock Frequency Detection

- Table 15. Example Digital Volume Settings

- Table 16. ATAPI Decode

- Table 17. Example ADC Input Gain Settings

- Table 18. TXP Output Selection

- Table 19. Receiver Input Selection

- Table 20. Auxiliary Data Width Selection

- 7. Parameter Definitions

- 8. Appendix A: External Filters

- 9. Appendix B: S/PDIF Receiver

- 10. Appendix C: PLL Filter

- 11. Appendix D: External AES3-S/PDIF-IEC60958 Receiver Components

- 12. Appendix E: ADC Filter Plots

- Figure 34. Single-Speed Mode Stopband Rejection

- Figure 35. Single-Speed Mode Transition Band

- Figure 36. Single-Speed Mode Transition Band (Detail)

- Figure 37. Single-Speed Mode Passband Ripple

- Figure 38. Double-Speed Mode Stopband Rejection

- Figure 39. Double-Speed Mode Transition Band

- Figure 40. Double-Speed Mode Transition Band (Detail)

- Figure 41. Double-Speed Mode Passband Ripple

- Figure 42. Quad-Speed Mode Stopband Rejection

- Figure 43. Quad-Speed Mode Transition Band

- Figure 44. Quad-Speed Mode Transition Band (Detail)

- Figure 45. Quad-Speed Mode Passband Ripple

- 13. Appendix F: DAC Filter Plots

- Figure 46. Single-Speed (fast) Stopband Rejection

- Figure 47. Single-Speed (fast) Transition Band

- Figure 48. Single-Speed (fast) Transition Band (detail)

- Figure 49. Single-Speed (fast) Passband Ripple

- Figure 50. Single-Speed (slow) Stopband Rejection

- Figure 51. Single-Speed (slow) Transition Band

- Figure 52. Single-Speed (slow) Transition Band (detail)

- Figure 53. Single-Speed (slow) Passband Ripple

- Figure 54. Double-Speed (fast) Stopband Rejection

- Figure 55. Double-Speed (fast) Transition Band

- Figure 56. Double-Speed (fast) Transition Band (detail)

- Figure 57. Double-Speed (fast) Passband Ripple

- Figure 58. Double-Speed (slow) Stopband Rejection

- Figure 59. Double-Speed (slow) Transition Band

- Figure 60. Double-Speed (slow) Transition Band (detail)

- Figure 61. Double-Speed (slow) Passband Ripple

- Figure 62. Quad-Speed (fast) Stopband Rejection

- Figure 63. Quad-Speed (fast) Transition Band

- Figure 64. Quad-Speed (fast) Transition Band (detail)

- Figure 65. Quad-Speed (fast) Passband Ripple

- Figure 66. Quad-Speed (slow) Stopband Rejection

- Figure 67. Quad-Speed (slow) Transition Band

- Figure 68. Quad-Speed (slow) Transition Band (detail)

- Figure 69. Quad-Speed (slow) Passband Ripple

- 14. Package Dimensions

- 15. Ordering Information

- 16. References

- 17. Revision History

DS583F2 25

CS42516

4.5.2 OMCK System Clock Mode

A special clock-switching mode is available that allows the clock that is input through the OMCK pin to be

used as the internal master clock. This feature is controlled by the SW_CTRLx bits in register “Clock Con-

trol (address 06h)” on page 52. An advanced auto-switching mode is also implemented to maintain mas-

ter clock functionality. The clock auto-switching mode allows the clock input through OMCK to be used as

a clock in the system without any disruption when the PLL loses lock, for example, when the input is re-

moved from the receiver. This clock-switching is done glitch-free. A clock adhering to the specifications

detailed in the Switching Characteristics table on page 11 must be applied to the OMCK pin at all times

that the FRC_PLL_LK bit is set to ‘0’ (See “Force PLL Lock (FRC_PLL_LK)” on page 53).

4.5.3 Master Mode

In Master Mode, the serial interface timings are derived from an external clock attached to OMCK or from

the output of the PLL with an input reference to either the S/PDIF Receiver recovered clock or the SAI_L-

RCK input from the Serial Audio Interface Port. Master clock selection and operation is configured with

the SW_CTRL1:0 bits in the Clock Control Register (See “Clock Control (address 06h)” on page 52).The

supported PLL output frequencies are shown in Table 2 below.

4.5.4 Slave Mode

In Slave Mode, CX_LRCK, CX_SCLK and/or SAI_LRCK, SAI_SCLK operate as inputs. The Left/Right

clock signal must be equal to the sample rate, Fs, and must be synchronously derived from the supplied

master clock, OMCK, or the output of the PLL. The serial bit clock, CX_SCLK and/or SAI_SCLK, must be

synchronously derived from the master clock and be equal to 128x, 64x, 48x or 32x Fs, depending on the

interface format selected and desired speed mode.

When the device is clocked from OMCK, the frequency of OMCK must be at least twice the frequency of

the fastest Slave Mode, SCLK. For example, if both serial ports are in Slave Mode with one SCLK running

at 32x Fs and the other at 64x Fs, the slowest OMCK signal that can be used to clock the device is

128x Fs.

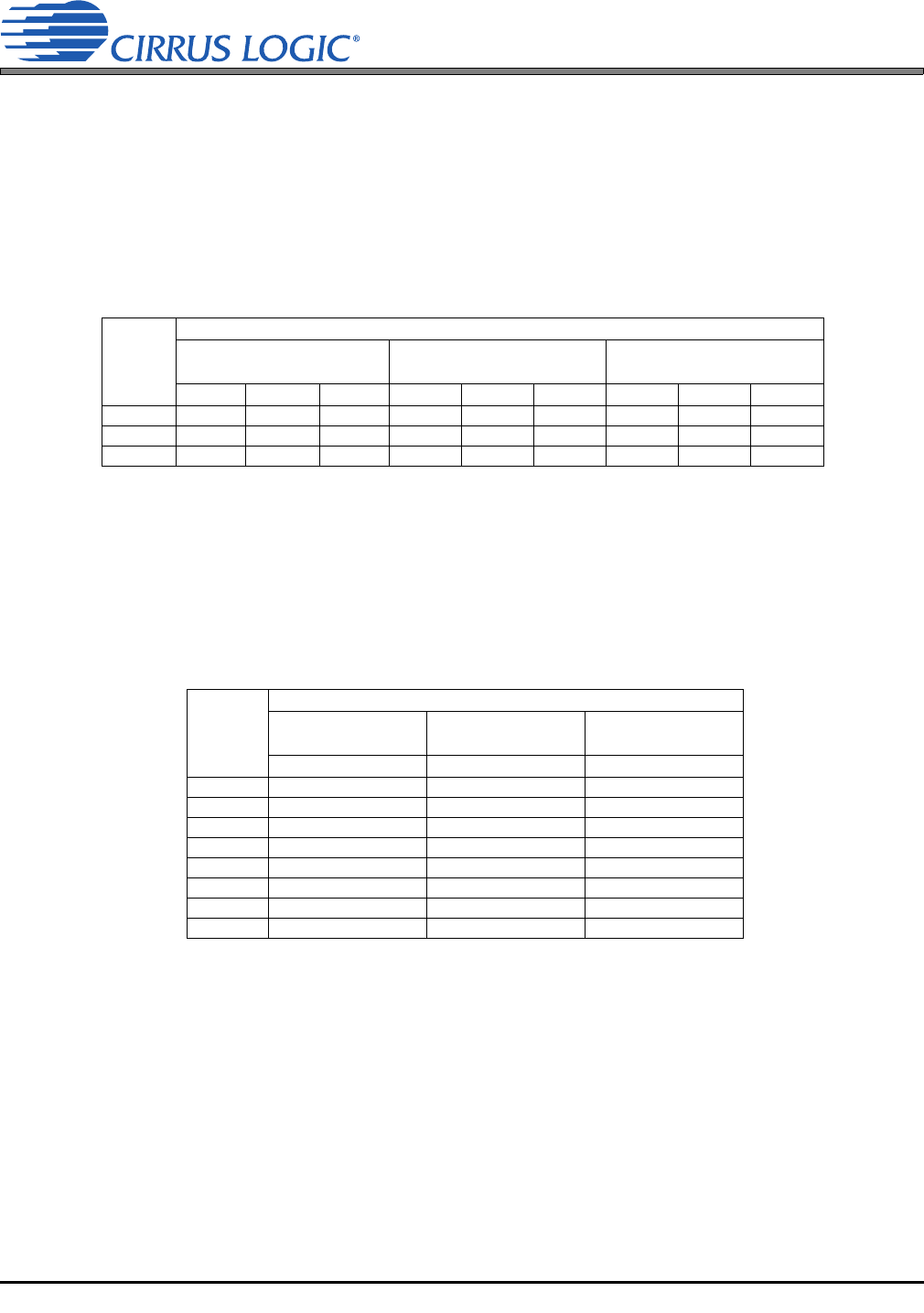

Sample

Rate

(kHz)

OMCK (MHz)

Single-Speed

(4 to 50 kHz)

Double-Speed

(50 to 100 kHz)

Quad-Speed

(100 to 192 kHz)

256x 384x 512x 128x 192x 256x 64x 96x 128x

48 12.2880 18.4320 24.5760 - - - - - -

96 - - - 12.2880 18.4320 24.5760 - - -

192 - - - - - - 12.2880 18.4320 24.5760

Table 1. Common OMCK Clock Frequencies

Sample

Rate

(kHz)

PLL Output (MHz)

Single Speed

(4 to 50 kHz)

Double Speed

(50 to 100 kHz)

Quad Speed

(100 to 192 kHz)

256x 256x 256x

32 8.1920 - -

44.1 11.2896 - -

48 12.2880 - -

64 - 16.3840 -

88.2 - 22.5792 -

96 - 24.5760 -

176.4 - - 45.1584

192 - - 49.1520

Table 2. Common PLL Output Clock Frequencies