User guide

Table Of Contents

- 1. Characteristics and Specifications

- Specified Operating Conditions

- Absolute Maximum Ratings

- Analog Input Characteristics

- A/D Digital Filter Characteristics

- Analog Output Characteristics

- D/A Digital Filter Characteristics

- Switching Characteristics

- Switching Characteristics - Control Port - I²C™ Format

- Switching Characteristics - Control Port - SPI™ Format

- DC Electrical Characteristics

- Digital Interface Characteristics

- 2. Pin Descriptions

- 3. Typical Connection Diagram

- 4. Applications

- 4.1 Overview

- 4.2 Analog Inputs

- 4.3 Analog Outputs

- 4.4 S/PDIF Receiver

- 4.5 Clock Generation

- 4.6 Digital Interfaces

- 4.7 Control Port Description and Timing

- 4.8 Interrupts

- 4.9 Reset and Power-Up

- 4.10 Power Supply, Grounding, and PCB Layout

- 5. Register Quick Reference

- 6. Register Description

- Table 5. DAC De-Emphasis

- Table 6. Receiver De-Emphasis

- Table 7. Digital Interface Formats

- Table 8. ADC One-Line Mode

- Table 9. DAC One-Line Mode

- Table 10. RMCK Divider Settings

- Table 11. OMCK Frequency Settings

- Table 12. Master Clock Source Select

- Table 13. AES Format Detection

- Table 14. Receiver Clock Frequency Detection

- Table 15. Example Digital Volume Settings

- Table 16. ATAPI Decode

- Table 17. Example ADC Input Gain Settings

- Table 18. TXP Output Selection

- Table 19. Receiver Input Selection

- Table 20. Auxiliary Data Width Selection

- 7. Parameter Definitions

- 8. Appendix A: External Filters

- 9. Appendix B: S/PDIF Receiver

- 10. Appendix C: PLL Filter

- 11. Appendix D: External AES3-S/PDIF-IEC60958 Receiver Components

- 12. Appendix E: ADC Filter Plots

- Figure 34. Single-Speed Mode Stopband Rejection

- Figure 35. Single-Speed Mode Transition Band

- Figure 36. Single-Speed Mode Transition Band (Detail)

- Figure 37. Single-Speed Mode Passband Ripple

- Figure 38. Double-Speed Mode Stopband Rejection

- Figure 39. Double-Speed Mode Transition Band

- Figure 40. Double-Speed Mode Transition Band (Detail)

- Figure 41. Double-Speed Mode Passband Ripple

- Figure 42. Quad-Speed Mode Stopband Rejection

- Figure 43. Quad-Speed Mode Transition Band

- Figure 44. Quad-Speed Mode Transition Band (Detail)

- Figure 45. Quad-Speed Mode Passband Ripple

- 13. Appendix F: DAC Filter Plots

- Figure 46. Single-Speed (fast) Stopband Rejection

- Figure 47. Single-Speed (fast) Transition Band

- Figure 48. Single-Speed (fast) Transition Band (detail)

- Figure 49. Single-Speed (fast) Passband Ripple

- Figure 50. Single-Speed (slow) Stopband Rejection

- Figure 51. Single-Speed (slow) Transition Band

- Figure 52. Single-Speed (slow) Transition Band (detail)

- Figure 53. Single-Speed (slow) Passband Ripple

- Figure 54. Double-Speed (fast) Stopband Rejection

- Figure 55. Double-Speed (fast) Transition Band

- Figure 56. Double-Speed (fast) Transition Band (detail)

- Figure 57. Double-Speed (fast) Passband Ripple

- Figure 58. Double-Speed (slow) Stopband Rejection

- Figure 59. Double-Speed (slow) Transition Band

- Figure 60. Double-Speed (slow) Transition Band (detail)

- Figure 61. Double-Speed (slow) Passband Ripple

- Figure 62. Quad-Speed (fast) Stopband Rejection

- Figure 63. Quad-Speed (fast) Transition Band

- Figure 64. Quad-Speed (fast) Transition Band (detail)

- Figure 65. Quad-Speed (fast) Passband Ripple

- Figure 66. Quad-Speed (slow) Stopband Rejection

- Figure 67. Quad-Speed (slow) Transition Band

- Figure 68. Quad-Speed (slow) Transition Band (detail)

- Figure 69. Quad-Speed (slow) Passband Ripple

- 14. Package Dimensions

- 15. Ordering Information

- 16. References

- 17. Revision History

16 DS583F2

CS42516

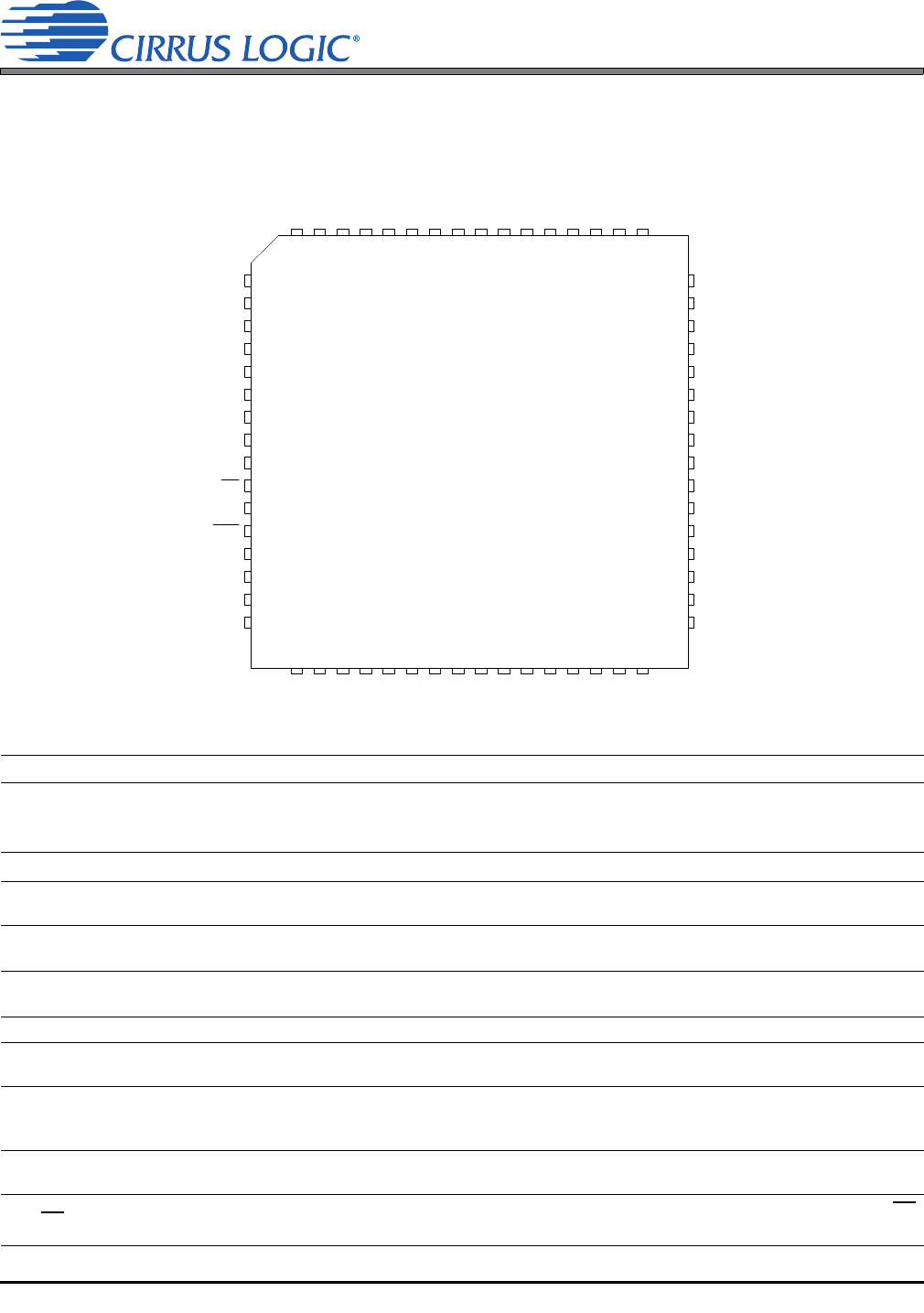

2. PIN DESCRIPTIONS

Pin Name # Pin Description

CX_SDIN1

CX_SDIN2

CX_SDIN3

1

64

63

Codec Serial Audio Data Input (Input) - Input for two’s complement serial audio data.

CX_SCLK

2

CODEC Serial Clock (Input/Output) - Serial clock for the CODEC serial audio interface.

CX_LRCK

3

CODEC Left Right Clock (Input/Output) - Determines which channel, Left or Right, is currently active on

the CODEC serial audio data line.

VD

4

51

Digital Power (Input) - Positive power supply for the digital section.

DGND

5

52

Digital Ground (Input) - Ground reference. Should be connected to digital ground.

VLC

6

Control Port Power (Input) - Determines the required signal level for the control port.

SCL/CCLK

7

Serial Control Port Clock (Input) - Serial clock for the serial control port. Requires an external pull-up

resistor to the logic interface voltage in I²C mode as shown in the Typical Connection Diagram.

SDA/CDOUT

8

Serial Control Data (Input/Output) - SDA is a data I/O line in I²C mode and requires an external pull-up

resistor to the logic interface voltage, as shown in the Typical Connection Diagram. CDOUT is the output

data line for the control port interface in SPI mode.

AD1/CDIN

9

Address Bit 1 (I²C)/Serial Control Data (SPI) (Input) - AD1 is a chip address pin in I²C mode; CDIN is

the input data line for the control port interface in SPI mode.

AD0/CS

10

Address Bit 0 (I²C)/Control Port Chip Select (SPI) (Input) - AD0 is a chip address pin in I²C mode; CS

is the chip select signal in SPI mode.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32

64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

CX_SDIN1

SAI_SCLK

SAI_LRCK

VD

DGND

VLC

SCL/CCLK

SDA/CDOUT

AD1/CDIN

AD0/CS

INT

RST

AINR-

AINR+

AINL+

AINL-

VQ

FILT+

REFGND

NC

NC

NC

NC

VA

AGND

AOUTB3-

AOUTB3+

AOUTA3+

AOUTA3-

AOUTB2-

AOUTB2+

AOUTA2+

AOUTA2-

AOUTB1-

AOUTB1+

AOUTA1+

AOUTA1-

MUTEC

AGND

VARX

RXP7/GPO7

RXP6/GPO6

RXP5/GPO5

RXP4/GPO4

RXP3/GPO3

RXP2/GPO2

RXP1/GPO1

LPFLT

RXP0

TXP

VD

DGND

VLS

SAI_SDOUT

RMCK

CX_SDOUT

ADCIN2

ADCIN1

OMCK

CX_LRCK

CX_SCLK

TEST

CX_SDIN3

CX_SDIN2

CS42516