Datasheet

Table Of Contents

- Features

- 1. Ordering Information

- 2. Typical Applications

- 3. Pinout and Block Diagram

- 4. Overview

- 5. Resources

- 6. Capacitive Touch Sensing

- 7. CPU

- 8. Memories

- 9. EDMA – Enhanced DMA Controller

- 10. Event System

- 11. System Clock and Clock options

- 11.1 Features

- 11.2 Overview

- 11.3 Clock Sources

- 11.3.1 32kHz Ultra Low Power Internal Oscillator

- 11.3.2 32.768kHz Calibrated Internal Oscillator

- 11.3.3 32.768kHz Crystal Oscillator

- 11.3.4 0.4 - 16MHz Crystal Oscillator

- 11.3.5 8MHz Calibrated Internal Oscillator

- 11.3.6 32MHz Run-time Calibrated Internal Oscillator

- 11.3.7 External Clock Sources

- 11.3.8 PLL with 1x-31x Multiplication Factor

- 12. Power Management and Sleep Modes

- 13. System Control and Reset

- 14. WDT – Watchdog Timer

- 15. Interrupts and Programmable Multilevel Interrupt Controller

- 16. I/O Ports

- 17. Timer Counter Type 4 and 5

- 18. WeX – Waveform Extension

- 19. Hi-Res – High Resolution Extension

- 20. Fault Extension

- 21. RTC – 16-bit Real-Time Counter

- 22. TWI – Two-Wire Interface

- 23. SPI – Serial Peripheral Interface

- 24. USART

- 25. IRCOM – IR Communication Module

- 26. XCL – XMEGA Custom Logic Module

- 27. CRC – Cyclic Redundancy Check Generator

- 28. ADC – 12-bit Analog to Digital Converter

- 29. DAC – Digital to Analog Converter

- 30. AC – Analog Comparator

- 31. Programming and Debugging

- 32. Pinout and Pin Functions

- 33. Peripheral Module Address Map

- 34. Instruction Set Summary

- 35. Packaging Information

- 36. Electrical Characteristics

- 36.1 Absolute Maximum Ratings

- 36.2 General Operating Ratings

- 36.3 Current Consumption

- 36.4 Wake-up Time from Sleep Modes

- 36.5 I/O Pin Characteristics

- 36.6 ADC Characteristics

- 36.7 DAC Characteristics

- 36.8 Analog Comparator Characteristics

- 36.9 Bandgap and Internal 1.0V Reference Characteristics

- 36.10 External Reset Characteristics

- 36.11 Power-on Reset Characteristics

- 36.12 Flash and EEPROM Characteristics

- 36.13 Clock and Oscillator Characteristics

- 36.13.1 Calibrated 32.768kHz Internal Oscillator Characteristics

- 36.13.2 Calibrated 8MHz Internal Oscillator Characteristics

- 36.13.3 Calibrated and Tunable 32MHz Internal Oscillator Characteristics

- 36.13.4 32 kHz Internal ULP Oscillator Characteristics

- 36.13.5 Internal Phase Locked Loop (PLL) Characteristics

- 36.13.6 External Clock Characteristics

- 36.13.7 External 16MHz Crystal Oscillator and XOSC Characteristics

- 36.13.8 External 32.768kHz Crystal Oscillator and TOSC Characteristics

- 36.14 SPI Characteristics

- 36.15 Two-Wire Interface Characteristics

- 37. Typical Characteristics

- 37.1 Current Consumption

- 37.2 I/O Pin Characteristics

- 37.3 ADC Characteristics

- 37.4 DAC Characteristics

- 37.5 AC Characteristics

- 37.6 Internal 1.0V Reference Characteristics

- 37.7 BOD Characteristics

- 37.8 External Reset Characteristics

- 37.9 Power-on Reset Characteristics

- 37.10 Oscillator Characteristics

- 37.11 Two-wire Interface Characteristics

- 37.12 PDI Characteristics

- 38. Errata – ATxmega32E5 / ATxmega16E5 / ATxmega8E5

- 39. Revision History

- Table of Contents

78

XMEGA E5 [DATASHEET]

Atmel-8153J–AVR-ATxmega8E5-ATxmega16E5-ATxmega32E5_Datasheet–11/2014

Notes: 1. Maximum numbers are based on characterisation and not tested in production, and valid for 10% to 90% input voltage range.

2. Unless otherwise noted all linearity, offset and gain error numbers are valid under the condition that external V

REF

is used.

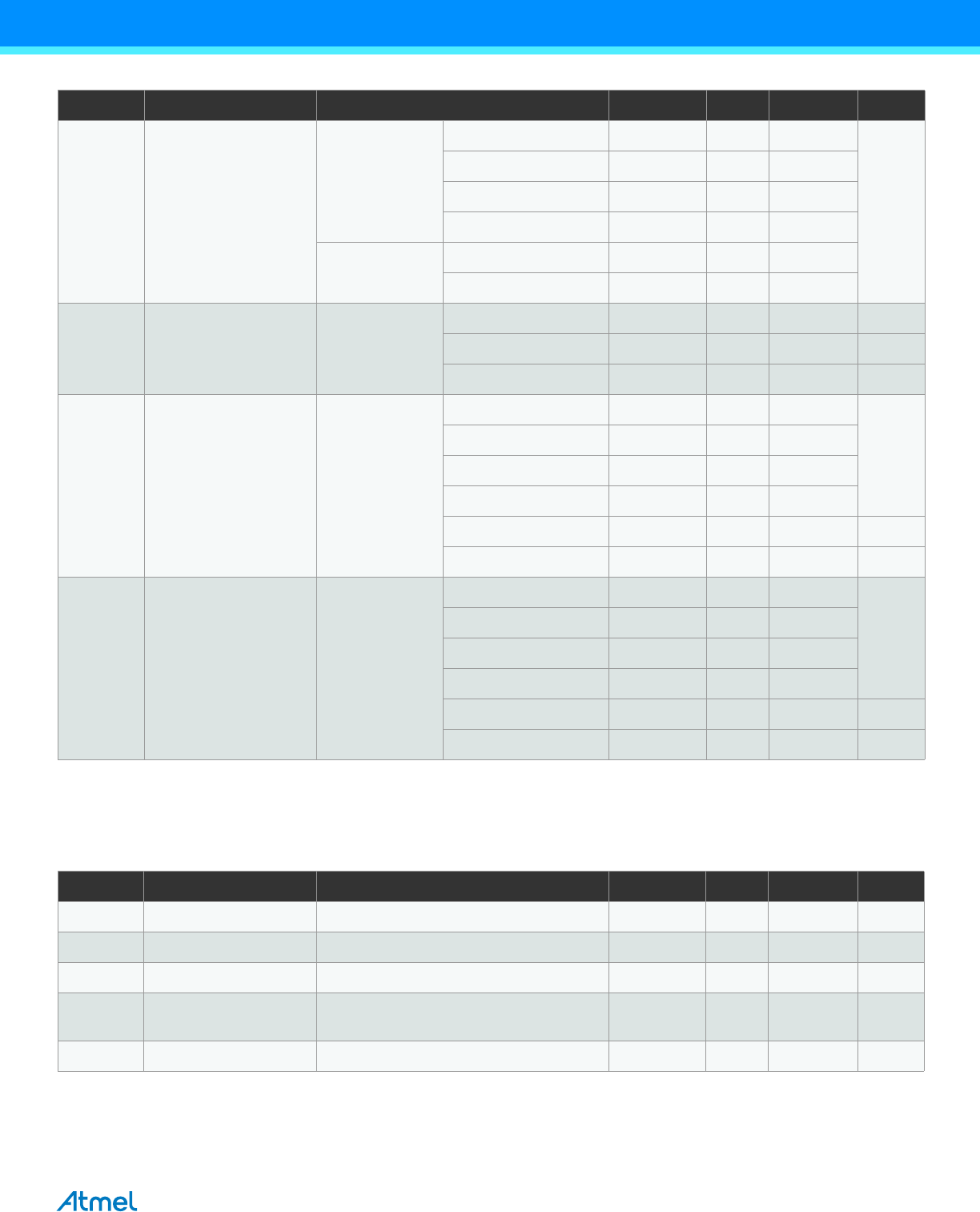

Table 36-10. Gain Stage Characteristics

DNL

(1)

Differential non-linearity

Differential

mode

16ksps, V

REF

= 3V 1

lsb

16ksps, V

REF

= 1V 2

300ksps, V

REF

= 3V 1

300ksps, V

REF

= 1V 2

Single ended

unsigned mode

16ksps, V

REF

= 3.0V 1 1.5

16ksps, V

REF

= 1.0V 2 3

Offset Error

Differential

mode

8 mV

Temperature drift 0.01 mV/K

Operating voltage drift 0.25 mV/V

Gain Error

Differential

mode

External reference -5

mV

AV

CC

/1.6 -5

AV

CC

/2.0 -6

Bandgap ±10

Temperature drift 0.02 mV/K

Operating voltage drift 2 mV/V

Gain Error

Single ended

unsigned mode

External reference -8

mV

AV

CC

/1.6 -8

AV

CC

/2.0 -8

Bandgap ±10

Temperature drift 0.03 mV/K

Operating voltage drift 2 mV/V

Symbol Parameter Condition

(2)

Min. Typ. Max. Units

Symbol Parameter Condition Min. Typ. Max. Units

R

in

Input resistance Switched 4.0 k

C

sample

Input capacitance Switched 4.4 pF

Signal range Gain stage output 0 AV

CC

- 0.6 V

Propagation delay ADC conversion rate 1/2 1 3

Clk

ADC

cycles

Clock rate Same as ADC 100 1800 kHz