Datasheet

Table Of Contents

- Features

- 1. Ordering Information

- 2. Typical Applications

- 3. Pinout and Block Diagram

- 4. Overview

- 5. Resources

- 6. Capacitive Touch Sensing

- 7. CPU

- 8. Memories

- 9. EDMA – Enhanced DMA Controller

- 10. Event System

- 11. System Clock and Clock options

- 11.1 Features

- 11.2 Overview

- 11.3 Clock Sources

- 11.3.1 32kHz Ultra Low Power Internal Oscillator

- 11.3.2 32.768kHz Calibrated Internal Oscillator

- 11.3.3 32.768kHz Crystal Oscillator

- 11.3.4 0.4 - 16MHz Crystal Oscillator

- 11.3.5 8MHz Calibrated Internal Oscillator

- 11.3.6 32MHz Run-time Calibrated Internal Oscillator

- 11.3.7 External Clock Sources

- 11.3.8 PLL with 1x-31x Multiplication Factor

- 12. Power Management and Sleep Modes

- 13. System Control and Reset

- 14. WDT – Watchdog Timer

- 15. Interrupts and Programmable Multilevel Interrupt Controller

- 16. I/O Ports

- 17. Timer Counter Type 4 and 5

- 18. WeX – Waveform Extension

- 19. Hi-Res – High Resolution Extension

- 20. Fault Extension

- 21. RTC – 16-bit Real-Time Counter

- 22. TWI – Two-Wire Interface

- 23. SPI – Serial Peripheral Interface

- 24. USART

- 25. IRCOM – IR Communication Module

- 26. XCL – XMEGA Custom Logic Module

- 27. CRC – Cyclic Redundancy Check Generator

- 28. ADC – 12-bit Analog to Digital Converter

- 29. DAC – Digital to Analog Converter

- 30. AC – Analog Comparator

- 31. Programming and Debugging

- 32. Pinout and Pin Functions

- 33. Peripheral Module Address Map

- 34. Instruction Set Summary

- 35. Packaging Information

- 36. Electrical Characteristics

- 36.1 Absolute Maximum Ratings

- 36.2 General Operating Ratings

- 36.3 Current Consumption

- 36.4 Wake-up Time from Sleep Modes

- 36.5 I/O Pin Characteristics

- 36.6 ADC Characteristics

- 36.7 DAC Characteristics

- 36.8 Analog Comparator Characteristics

- 36.9 Bandgap and Internal 1.0V Reference Characteristics

- 36.10 External Reset Characteristics

- 36.11 Power-on Reset Characteristics

- 36.12 Flash and EEPROM Characteristics

- 36.13 Clock and Oscillator Characteristics

- 36.13.1 Calibrated 32.768kHz Internal Oscillator Characteristics

- 36.13.2 Calibrated 8MHz Internal Oscillator Characteristics

- 36.13.3 Calibrated and Tunable 32MHz Internal Oscillator Characteristics

- 36.13.4 32 kHz Internal ULP Oscillator Characteristics

- 36.13.5 Internal Phase Locked Loop (PLL) Characteristics

- 36.13.6 External Clock Characteristics

- 36.13.7 External 16MHz Crystal Oscillator and XOSC Characteristics

- 36.13.8 External 32.768kHz Crystal Oscillator and TOSC Characteristics

- 36.14 SPI Characteristics

- 36.15 Two-Wire Interface Characteristics

- 37. Typical Characteristics

- 37.1 Current Consumption

- 37.2 I/O Pin Characteristics

- 37.3 ADC Characteristics

- 37.4 DAC Characteristics

- 37.5 AC Characteristics

- 37.6 Internal 1.0V Reference Characteristics

- 37.7 BOD Characteristics

- 37.8 External Reset Characteristics

- 37.9 Power-on Reset Characteristics

- 37.10 Oscillator Characteristics

- 37.11 Two-wire Interface Characteristics

- 37.12 PDI Characteristics

- 38. Errata – ATxmega32E5 / ATxmega16E5 / ATxmega8E5

- 39. Revision History

- Table of Contents

63

XMEGA E5 [DATASHEET]

Atmel-8153J–AVR-ATxmega8E5-ATxmega16E5-ATxmega32E5_Datasheet–11/2014

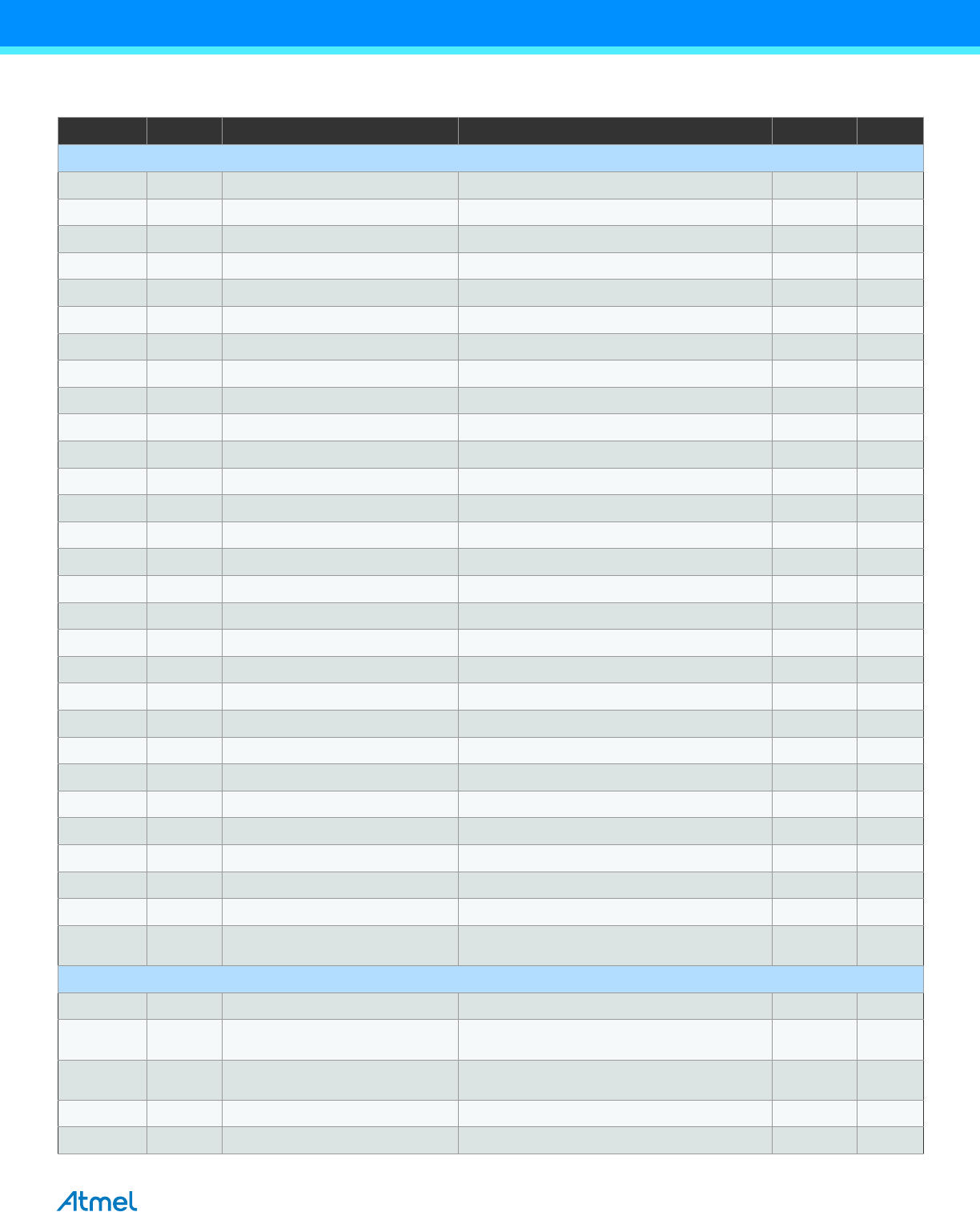

34. Instruction Set Summary

Mnemonics Operands Description Operation Flags #Clocks

Arithmetic and Logic Instructions

ADD Rd, Rr Add without Carry

Rd

Rd + Rr Z,C,N,V,S,H 1

ADC Rd, Rr Add with Carry Rd

Rd + Rr + C Z,C,N,V,S,H 1

ADIW Rd, K Add Immediate to Word Rd

Rd + 1:Rd + K Z,C,N,V,S 2

SUB Rd, Rr Subtract without Carry Rd

Rd - Rr Z,C,N,V,S,H 1

SUBI Rd, K Subtract Immediate Rd

Rd - K Z,C,N,V,S,H 1

SBC Rd, Rr Subtract with Carry Rd

Rd - Rr - C Z,C,N,V,S,H 1

SBCI Rd, K Subtract Immediate with Carry Rd

Rd - K - C Z,C,N,V,S,H 1

SBIW Rd, K Subtract Immediate from Word Rd + 1:Rd

Rd + 1:Rd - K Z,C,N,V,S 2

AND Rd, Rr Logical AND Rd

Rd Rr Z,N,V,S 1

ANDI Rd, K Logical AND with Immediate Rd

Rd K Z,N,V,S 1

OR Rd, Rr Logical OR Rd

Rd v Rr Z,N,V,S 1

ORI Rd, K Logical OR with Immediate Rd

Rd v K Z,N,V,S 1

EOR Rd, Rr Exclusive OR Rd

Rd Rr Z,N,V,S 1

COM Rd One’s Complement Rd

$FF - Rd Z,C,N,V,S 1

NEG Rd Two’s Complement Rd

$00 - Rd Z,C,N,V,S,H 1

SBR Rd,K Set Bit(s) in Register Rd

Rd v K Z,N,V,S 1

CBR Rd,K Clear Bit(s) in Register Rd

Rd ($FFh - K) Z,N,V,S 1

INC Rd Increment Rd

Rd + 1 Z,N,V,S 1

DEC Rd Decrement Rd

Rd - 1 Z,N,V,S 1

TST Rd Test for Zero or Minus Rd

Rd Rd Z,N,V,S 1

CLR Rd Clear Register Rd

Rd Rd Z,N,V,S 1

SER Rd Set Register Rd

$FF None 1

MUL Rd,Rr Multiply Unsigned R1:R0

Rd x Rr (UU) Z,C 2

MULS Rd,Rr Multiply Signed R1:R0

Rd x Rr (SS) Z,C 2

MULSU Rd,Rr Multiply Signed with Unsigned R1:R0

Rd x Rr (SU) Z,C 2

FMUL Rd,Rr Fractional Multiply Unsigned R1:R0

Rd x Rr<<1 (UU) Z,C 2

FMULS Rd,Rr Fractional Multiply Signed R1:R0

Rd x Rr<<1 (SS) Z,C 2

FMULSU Rd,Rr Fractional Multiply Signed with Unsigned R1:R0

Rd x Rr<<1 (SU) Z,C 2

DES K Data Encryption

if (H = 0) then R15:R0

else if (H = 1) then R15:R0

Encrypt(R15:R0, K)

Decrypt(R15:R0, K)

1/2

Branch instructions

RJMP k Relative Jump PC

PC + k + 1 None 2

IJMP Indirect Jump to (Z)

PC(15:0)

PC(21:16)

Z,

0

None 2

EIJMP Extended Indirect Jump to (Z)

PC(15:0)

PC(21:16)

Z,

EIND

None 2

JMP k Jump PC

k None 3

RCALL k Relative Call Subroutine PC

PC + k + 1 None 2 / 3

(1)