Datasheet

Table Of Contents

- FEATURES

- APPLICATIONS

- FUNCTIONAL BLOCK DIAGRAM

- TABLE OF CONTENTS

- SPECIFICATIONS

- ABSOLUTE MAXIMUM RATINGS

- PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

- GENERAL DESCRIPTION

- TYPICAL PERFORMANCE CHARACTERISTICS

- FEATURES

- COLOR BAR GENERATION

- SQUARE PIXEL MODE

- COLOR SIGNAL CONTROL

- BURST SIGNAL CONTROL

- NTSC PEDESTAL CONTROL

- PIXEL TIMING DESCRIPTION

- SUBCARRIER RESET

- REAL-TIME CONTROL

- Video Timing Description

- Vertical Blanking Data Insertion

- Mode 0 (CCIR-656): Slave Option

- Mode 0 (CCIR-656): Master Option

- Mode 1: Slave Option HSYNC, BLANK, FIELD

- Mode 1: Master Option HSYNC, BLANK, FIELD

- Mode 2: Slave Option HSYNC, VSYNC, BLANK

- Mode 2: Master Option HSYNC, VSYNC, BLANK

- Mode 3: Master/Slave Option HSYNC, BLANK, FIELD

- POWER-ON RESET

- SCH PHASE MODE

- MPU PORT DESCRIPTION

- REGISTER ACCESSES

- REGISTER PROGRAMMING

- SUBADDRESS REGISTER (SR7–SR0)

- REGISTER SELECT (SR5–SR0)

- MODE REGISTER 1 (MR1)

- MODE REGISTER 2 (MR2)

- MODE REGISTER 3 (MR3)

- MODE REGISTER 4 (MR4)

- TIMING MODE REGISTER 0 (TR0)

- TIMING MODE REGISTER 1 (TR1)

- SUBCARRIER FREQUENCY REGISTERS 3–0

- SUBCARRIER PHASE REGISTER

- CLOSED CAPTIONING EVEN FIELD DATA REGISTERS 1–0

- CLOSED CAPTIONING ODD FIELD DATA REGISTERS 1–0

- NTSC PEDESTAL/PAL TELETEXT CONTROL REGISTERS 3–0

- TELETEXT REQUEST CONTROL REGISTER (TC07)

- CGMS_WSS REGISTER 0 (C/W0)

- CGMS_WSS REGISTER 1 (C/W1)

- CGMS_WSS REGISTER 2 (C/W2)

- APPENDIX 1—BOARD DESIGN AND LAYOUT CONSIDERATIONS

- APPENDIX 2—CLOSED CAPTIONING

- APPENDIX 3—COPY GENERATION MANAGEMENT SYSTEM (CGMS)

- APPENDIX 4—WIDE SCREEN SIGNALING (WSS)

- APPENDIX 5—TELETEXT

- APPENDIX 6—WAVEFORMS

- APPENDIX 7—OPTIONAL OUTPUT FILTER

- APPENDIX 8—RECOMMENDED REGISTER VALUES

- OUTLINE DIMENSIONS

ADV7174/ADV7179

Rev. B | Page 43 of 52

APPENDIX 4—WIDE SCREEN SIGNALING (WSS)

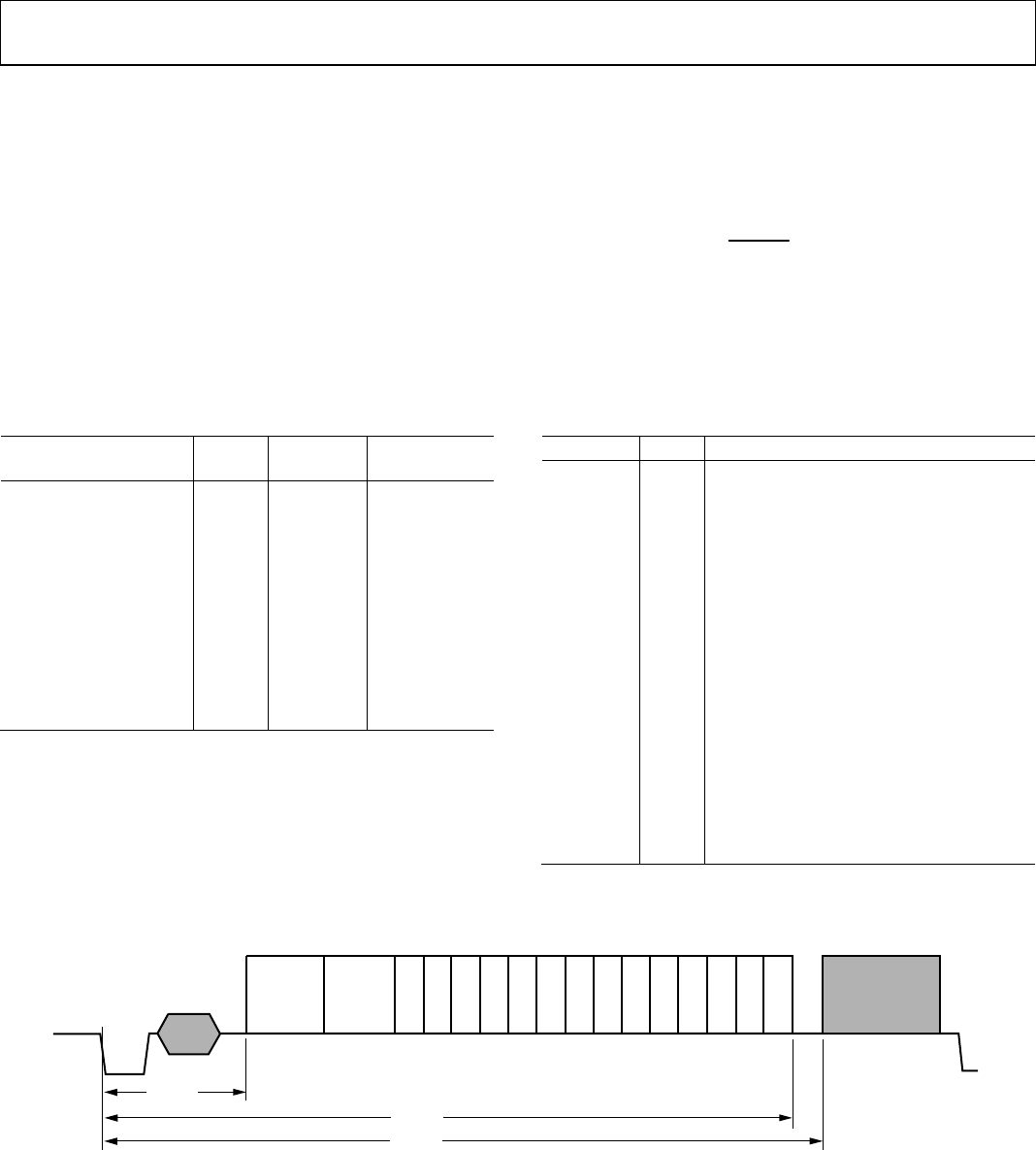

The ADV7174/ADV7179 supports WSS, conforming to the

standard. WSS data is transmitted on Line 23. WSS data can

only be transmitted when the ADV7174/ ADV7179 is

configured in PAL mode. The WSS data is 14 bits long, the

function of each of these bits is as shown below. The WSS data

is preceded by a run-in sequence and a start code (see Figure 58).

The bits are output from the configuration registers in the

following order: C/W20 = W0, C/W21 = W1, C/W22 = W2,

C/W23 = W3, C/W24 = W4, C/W25 = W5, C/W26 = W6,

C/W27 = W7, C/W10 = W8, C/W11 = W9, C/W12 = W10,

C/W13 = W11, C/W14 = W12, C/W15 = W13. If the Bit

C/W07 is set to a Logic 1, it enables the WSS data to be

transmitted on Line 23. The latter portion of Line 23 (42.5 μs

from the falling edge of

HSYNC

) is available for the insertion of

video.

FUNCTION OF WSS BITS

Table 22. Bit 0–Bit 2 Bit 3 is the odd parity check of Bit 0–Bit 2

B0 B1 B2 B3

Aspect

Ratio

Format Position

0 0 0 1 4:3

Full

Format

Not

Applicable

1 0 0 0 14:9 Letterbox Center

0 1 0 0 14:9 Letterbox Top

1 1 0 1 16:9 Letterbox Center

0 0 1 0 16:9 Letterbox Top

1 0 1 1 >16:9 Letterbox Center

0 1 1 1 14:9

Full

Format

Center

1 1 1 0 16:9

Not

Applicable

Not

Applicable

Table 23. Bit 4–Bit 7

Bit Value Description

B4 0

1

Camera Mode

Film Mode

B5 0

1

Standard Coding

Motion Adaptive Color Plus

B6 0

1

No Helper

Modulated Helper

B7

Reserved

B8 0

1

No Teletext Subtitles

Teletext Subtitles

B9–B10 0, 0

No Open Subtitles

1, 0 Subtitles in Active Image Area

0, 1

Subtitles out of Active Image Area

1, 1

Reserved

B11 0

1

No Surround Sound Information

Surround Sound Mode

B12

Reserved

B13 Reserved

11.0μs

W0 W1 W2 W3 W4 W5 W6 W7 W8 W9 W10 W11 W12 W13

500mV

RUN-IN

SEQUENCE

START

CODE

ACTIVE

VIDEO

02980-A-057

38.4μs

42.5μs

Figure 58. WSS Waveform Diagram