Datasheet

Table Of Contents

- FEATURES

- APPLICATIONS

- FUNCTIONAL BLOCK DIAGRAM

- TABLE OF CONTENTS

- SPECIFICATIONS

- ABSOLUTE MAXIMUM RATINGS

- PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

- GENERAL DESCRIPTION

- TYPICAL PERFORMANCE CHARACTERISTICS

- FEATURES

- COLOR BAR GENERATION

- SQUARE PIXEL MODE

- COLOR SIGNAL CONTROL

- BURST SIGNAL CONTROL

- NTSC PEDESTAL CONTROL

- PIXEL TIMING DESCRIPTION

- SUBCARRIER RESET

- REAL-TIME CONTROL

- Video Timing Description

- Vertical Blanking Data Insertion

- Mode 0 (CCIR-656): Slave Option

- Mode 0 (CCIR-656): Master Option

- Mode 1: Slave Option HSYNC, BLANK, FIELD

- Mode 1: Master Option HSYNC, BLANK, FIELD

- Mode 2: Slave Option HSYNC, VSYNC, BLANK

- Mode 2: Master Option HSYNC, VSYNC, BLANK

- Mode 3: Master/Slave Option HSYNC, BLANK, FIELD

- POWER-ON RESET

- SCH PHASE MODE

- MPU PORT DESCRIPTION

- REGISTER ACCESSES

- REGISTER PROGRAMMING

- SUBADDRESS REGISTER (SR7–SR0)

- REGISTER SELECT (SR5–SR0)

- MODE REGISTER 1 (MR1)

- MODE REGISTER 2 (MR2)

- MODE REGISTER 3 (MR3)

- MODE REGISTER 4 (MR4)

- TIMING MODE REGISTER 0 (TR0)

- TIMING MODE REGISTER 1 (TR1)

- SUBCARRIER FREQUENCY REGISTERS 3–0

- SUBCARRIER PHASE REGISTER

- CLOSED CAPTIONING EVEN FIELD DATA REGISTERS 1–0

- CLOSED CAPTIONING ODD FIELD DATA REGISTERS 1–0

- NTSC PEDESTAL/PAL TELETEXT CONTROL REGISTERS 3–0

- TELETEXT REQUEST CONTROL REGISTER (TC07)

- CGMS_WSS REGISTER 0 (C/W0)

- CGMS_WSS REGISTER 1 (C/W1)

- CGMS_WSS REGISTER 2 (C/W2)

- APPENDIX 1—BOARD DESIGN AND LAYOUT CONSIDERATIONS

- APPENDIX 2—CLOSED CAPTIONING

- APPENDIX 3—COPY GENERATION MANAGEMENT SYSTEM (CGMS)

- APPENDIX 4—WIDE SCREEN SIGNALING (WSS)

- APPENDIX 5—TELETEXT

- APPENDIX 6—WAVEFORMS

- APPENDIX 7—OPTIONAL OUTPUT FILTER

- APPENDIX 8—RECOMMENDED REGISTER VALUES

- OUTLINE DIMENSIONS

ADV7174/ADV7179

Rev. B | Page 35 of 52

SUBCARRIER FREQUENCY REGISTERS 3–0

Bits: FSC3–FSC0

Address: SR4–SR00 = 09H–0CH

These 8-bit-wide registers are used to set up the subcarrier frequency. The value of these registers is calculated by using the following

equation:

*2

32

×

Line Video One in Cycles Clock MHz 27 of No.

Line Video of Line One in ValuesFrequencyr Subcarrieof No.

* Rounded to the nearest integer.

For example, in NTSC mode,

Eh1C07F21d5694085422

1716

5.227

32

==×=ValueFrequencySubcarrier

Note that on power-up, F

SC

Register 0 is set to 16h. A value of 1E as derived above is recommended.

Program as

F

SC

Register 0: 1EH

F

SC

Register 2: 7CH

F

SC

Register 3: F0H

F

SC

Register 4: 21H

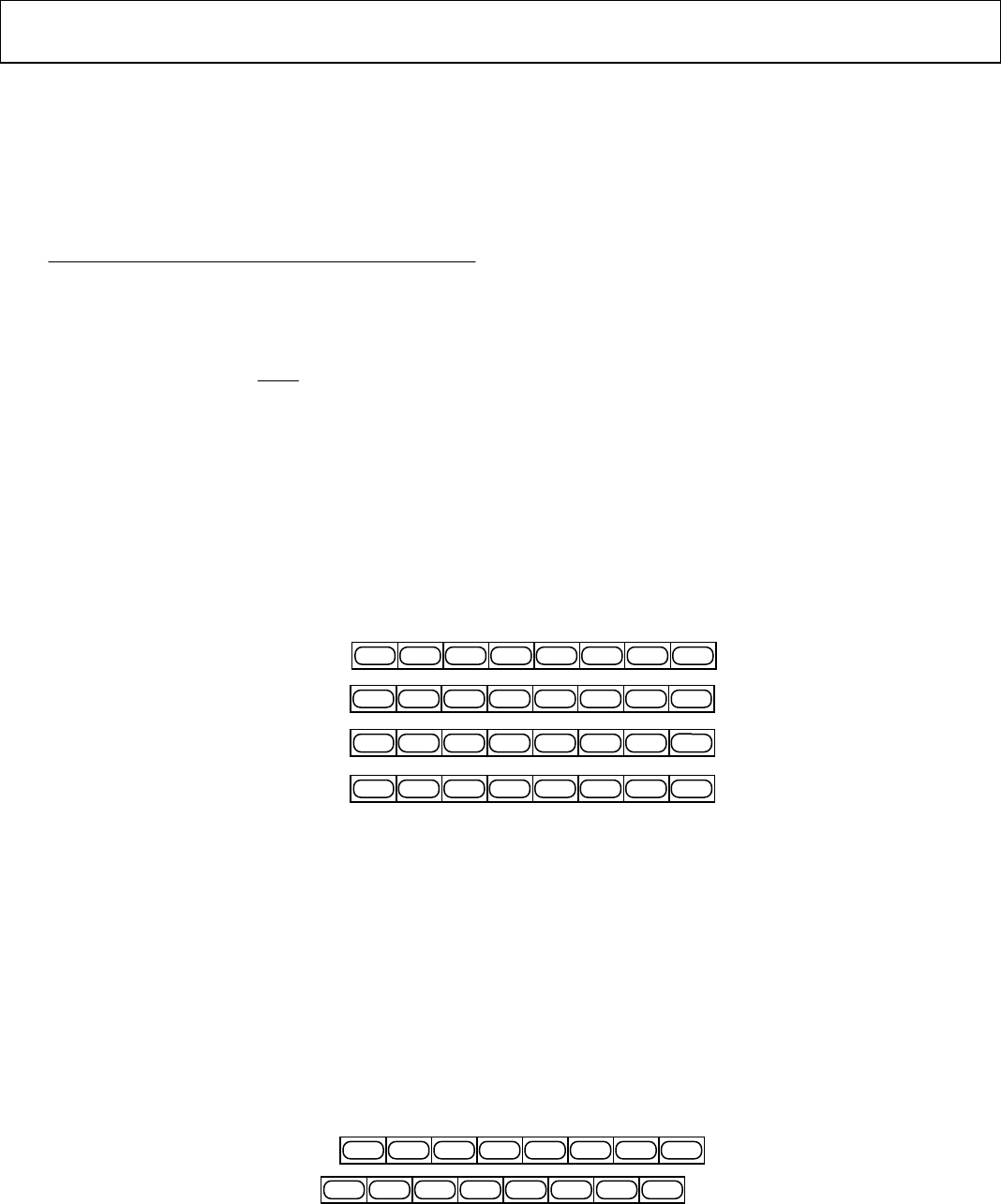

Figure 45 shows how the frequency is set up by the four registers.

SUBCARRIER

FREQUENCY

REG 3

S

UBCARRIE

R

FREQUENCY

REG 2

S

UBCARRIE

R

FREQUENCY

REG 1

S

UBCARRIE

R

FREQUENCY

REG 0

FSC30

FSC29 FSC27 FSC25FSC28 FSC24FSC31 FSC26

FSC22 FSC21 FSC19 FSC17FSC20 FSC16FSC23 FSC18

FSC14

FSC13 FSC11 FSC9FSC12

FSC8

FSC15 FSC10

FSC6

FSC5 FSC3 FSC1FSC4 FSC0FSC7 FSC2

02980-A-044

Figure 45. Subcarrier Frequency Register

SUBCARRIER PHASE REGISTER

Bits: FP7–FP0

Address: SR4–SR0 = 0DH

This 8-bit-wide register is used to set up the subcarrier phase. Each bit represents 1.41°. For normal operation, this register is set to 00H.

CLOSED CAPTIONING EVEN FIELD DATA REGISTERS 1–0

Bits: CED15–CED0

Address: SR4–SR0 = 0EH–0FH

These 8-bit-wide registers are used to set up the closed captioning extended data bytes on even fields. Figure 46 shows how the high and

low bytes are set up in the registers.

BYTE 1

BYTE 0

CED6 CED5 CED3 CED1CED4 CED2 CED0CED7

CED14 CED13 CED11 CED9CED12 CED10 CED8CED15

002980-A-045

Figure 46. Closed Captioning Extended Data Register