Datasheet

Table Of Contents

- FEATURES

- APPLICATIONS

- FUNCTIONAL BLOCK DIAGRAM

- TABLE OF CONTENTS

- SPECIFICATIONS

- ABSOLUTE MAXIMUM RATINGS

- PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

- GENERAL DESCRIPTION

- TYPICAL PERFORMANCE CHARACTERISTICS

- FEATURES

- COLOR BAR GENERATION

- SQUARE PIXEL MODE

- COLOR SIGNAL CONTROL

- BURST SIGNAL CONTROL

- NTSC PEDESTAL CONTROL

- PIXEL TIMING DESCRIPTION

- SUBCARRIER RESET

- REAL-TIME CONTROL

- Video Timing Description

- Vertical Blanking Data Insertion

- Mode 0 (CCIR-656): Slave Option

- Mode 0 (CCIR-656): Master Option

- Mode 1: Slave Option HSYNC, BLANK, FIELD

- Mode 1: Master Option HSYNC, BLANK, FIELD

- Mode 2: Slave Option HSYNC, VSYNC, BLANK

- Mode 2: Master Option HSYNC, VSYNC, BLANK

- Mode 3: Master/Slave Option HSYNC, BLANK, FIELD

- POWER-ON RESET

- SCH PHASE MODE

- MPU PORT DESCRIPTION

- REGISTER ACCESSES

- REGISTER PROGRAMMING

- SUBADDRESS REGISTER (SR7–SR0)

- REGISTER SELECT (SR5–SR0)

- MODE REGISTER 1 (MR1)

- MODE REGISTER 2 (MR2)

- MODE REGISTER 3 (MR3)

- MODE REGISTER 4 (MR4)

- TIMING MODE REGISTER 0 (TR0)

- TIMING MODE REGISTER 1 (TR1)

- SUBCARRIER FREQUENCY REGISTERS 3–0

- SUBCARRIER PHASE REGISTER

- CLOSED CAPTIONING EVEN FIELD DATA REGISTERS 1–0

- CLOSED CAPTIONING ODD FIELD DATA REGISTERS 1–0

- NTSC PEDESTAL/PAL TELETEXT CONTROL REGISTERS 3–0

- TELETEXT REQUEST CONTROL REGISTER (TC07)

- CGMS_WSS REGISTER 0 (C/W0)

- CGMS_WSS REGISTER 1 (C/W1)

- CGMS_WSS REGISTER 2 (C/W2)

- APPENDIX 1—BOARD DESIGN AND LAYOUT CONSIDERATIONS

- APPENDIX 2—CLOSED CAPTIONING

- APPENDIX 3—COPY GENERATION MANAGEMENT SYSTEM (CGMS)

- APPENDIX 4—WIDE SCREEN SIGNALING (WSS)

- APPENDIX 5—TELETEXT

- APPENDIX 6—WAVEFORMS

- APPENDIX 7—OPTIONAL OUTPUT FILTER

- APPENDIX 8—RECOMMENDED REGISTER VALUES

- OUTLINE DIMENSIONS

ADV7174/ADV7179

Rev. B | Page 31 of 52

MODE REGISTER 3 (MR3)

Bits: MR37–MR30

Address: SR4–SR0 = 03H

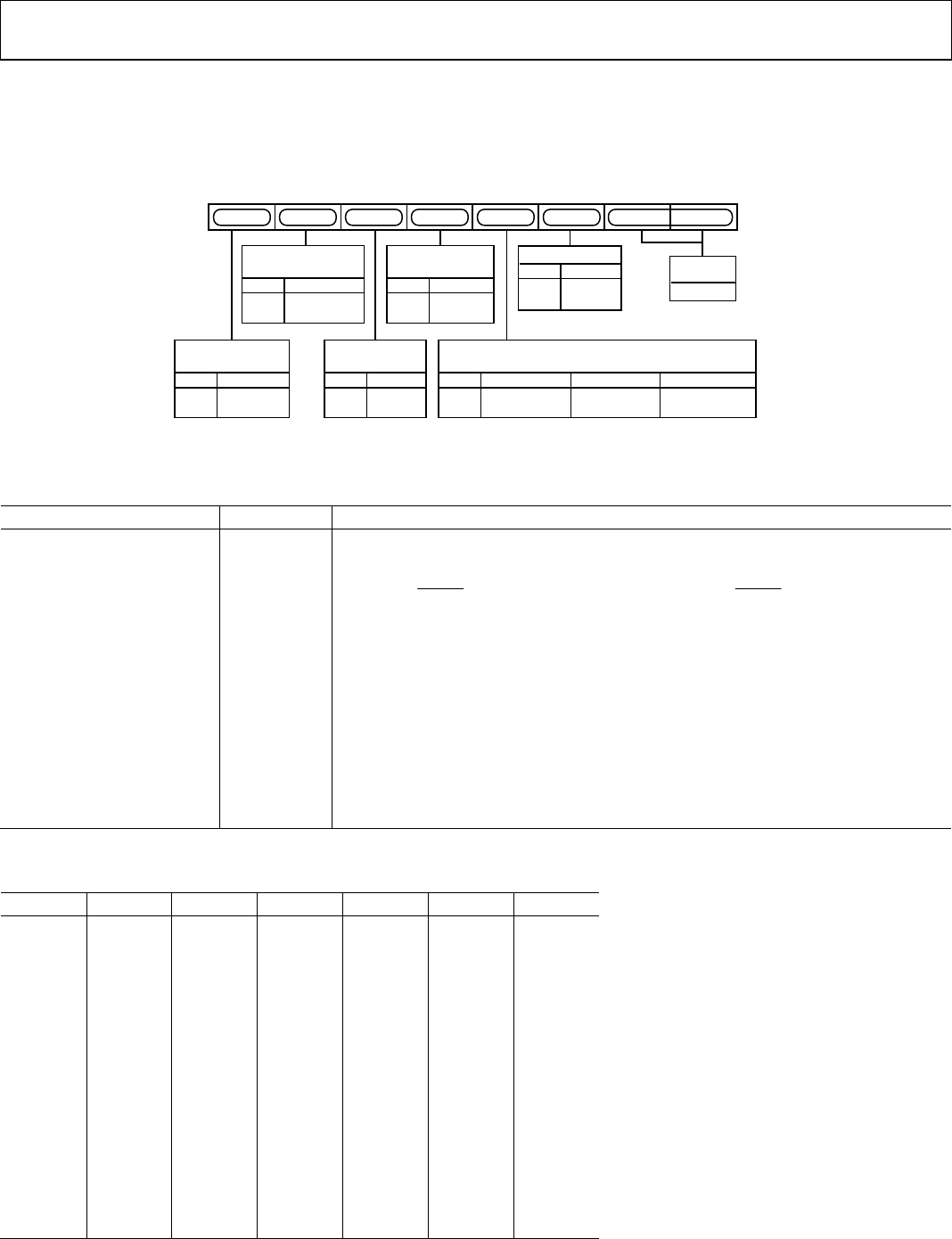

Mode Register 3 is an 8-bit-wide register. Figure 41 shows the various operations under the control of Mode Register 3.

MR31

MR30

MR37

MR32MR34 MR33MR35MR36

MR30

MR31

RESERVED

VBI_OPEN

0 DISABLE

1 ENABLE

MR32

DAC OUTPUT

0 COMPOSITE

1 GREEN/LUMA/Y

MR33

DAC A

BLUE/COMP/Pb

BLUE/COMP/Pb

DAC B

RED/CHROMA/Pr

RED/CHROMA/Pr

DAC C

CHROMA OUTPUT

SELECT

0 DISABLE

1 ENABLE

MR34

TELETEXT

ENABLE

0 DISABLE

1 ENABLE

MR35

TTXREQ BIT

MODE CONTROL

0 NORMAL

1 BIT REQUEST

MR36

INPUT DEFAULT

COLOR

0 DISABLE

1 ENABLE

MR37

02980-A-040

Figure 41. Mode Register 3

Table 12. MR3 Bit Description

Bit Name Bit No. Description

Revision Code MR30–MR31 These bits are read-only and indicate the revision of the device.

VBI Open MR32

This bit determines whether or not data in the vertical blanking interval (VBI) is output to

the analog outputs or blanked. VBI data insertion is not available in Slave Mode 0. Also,

when both

BLANK

input control and VBI open are enabled,

BLANK

input control has

priority, i.e., VBI data insertion will not work.

DAC Output MR33

This bit is used to switch the DAC outputs from SCART to a EUROSCART configuration. A

complete list of all DAC output configurations is shown in Table 13.

Chroma Output Select MR34

With this active high bit it is possible to output an extra chrominance signal C, on DAC A

in any configuration that features a CVBS signal.

Teletext Enable MR35

This bit must be set to 1 to enable Teletext data insertion on the TTX pin.

TTXREQ Bit Mode Control MR36

This bit enables switching of the Teletext request signal from a continuous high signal

(MR36 = 0) to a bitwise request signal (MR36 = 1).

Input Default Color MR37

This bit determines the default output color from the DACs for zero input pixel data (or

disconnected). A Logic 0 means that the color corresponding to 00000000 is displayed. A

Logic 1 forces the output color to black for 00000000 pixel input video data.

Table 13. DAC Output Configuration Matrix

MR34 MR40 MR41 MR33 DAC A DAC B DAC C

0 0 0 0 CVBS CVBS C

CVBS: Composite Video Baseband Signal

Y: Luminance Component Signal (For YPbPr or Y/C Mode)

C: Chrominance Signal (For Y/C Mode)

Pb: ColorComponent Signal (For YPbPr Mode)

Pr: Color Component Signal (For YPbPr Mode)

R: RED Component Video (For RGB Mode)

G: GREEN Component Video (For RGB Mode)

B: BLUE Component Video (For RGB Mode)

Each DAC can be powered on or off individually

See MR1 Description and Figure 39.

0 0 0 1 Y CVBS C

0 0 1 0 CVBS CVBS C

0 0 1 1 Y CVBS C

0 1 0 0 CVBS B R

0 1 0 1 G B R

0 1 1 0 CVBS Pb Pr

0 1 1 1 Y Pb Pr

1 0 0 0 C CVBS C

1 0 0 1 Y CVBS C

1 0 1 0 C CVBS C

1 0 1 1 Y CVBS C

1 1 0 0 C B R

1 1 0 1 G B R

1 1 1 0 C Pb Pr

1 1 1 1 Y Pb Pr