Datasheet

Table Of Contents

- FEATURES

- APPLICATIONS

- FUNCTIONAL BLOCK DIAGRAM

- TABLE OF CONTENTS

- SPECIFICATIONS

- ABSOLUTE MAXIMUM RATINGS

- PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

- GENERAL DESCRIPTION

- TYPICAL PERFORMANCE CHARACTERISTICS

- FEATURES

- COLOR BAR GENERATION

- SQUARE PIXEL MODE

- COLOR SIGNAL CONTROL

- BURST SIGNAL CONTROL

- NTSC PEDESTAL CONTROL

- PIXEL TIMING DESCRIPTION

- SUBCARRIER RESET

- REAL-TIME CONTROL

- Video Timing Description

- Vertical Blanking Data Insertion

- Mode 0 (CCIR-656): Slave Option

- Mode 0 (CCIR-656): Master Option

- Mode 1: Slave Option HSYNC, BLANK, FIELD

- Mode 1: Master Option HSYNC, BLANK, FIELD

- Mode 2: Slave Option HSYNC, VSYNC, BLANK

- Mode 2: Master Option HSYNC, VSYNC, BLANK

- Mode 3: Master/Slave Option HSYNC, BLANK, FIELD

- POWER-ON RESET

- SCH PHASE MODE

- MPU PORT DESCRIPTION

- REGISTER ACCESSES

- REGISTER PROGRAMMING

- SUBADDRESS REGISTER (SR7–SR0)

- REGISTER SELECT (SR5–SR0)

- MODE REGISTER 1 (MR1)

- MODE REGISTER 2 (MR2)

- MODE REGISTER 3 (MR3)

- MODE REGISTER 4 (MR4)

- TIMING MODE REGISTER 0 (TR0)

- TIMING MODE REGISTER 1 (TR1)

- SUBCARRIER FREQUENCY REGISTERS 3–0

- SUBCARRIER PHASE REGISTER

- CLOSED CAPTIONING EVEN FIELD DATA REGISTERS 1–0

- CLOSED CAPTIONING ODD FIELD DATA REGISTERS 1–0

- NTSC PEDESTAL/PAL TELETEXT CONTROL REGISTERS 3–0

- TELETEXT REQUEST CONTROL REGISTER (TC07)

- CGMS_WSS REGISTER 0 (C/W0)

- CGMS_WSS REGISTER 1 (C/W1)

- CGMS_WSS REGISTER 2 (C/W2)

- APPENDIX 1—BOARD DESIGN AND LAYOUT CONSIDERATIONS

- APPENDIX 2—CLOSED CAPTIONING

- APPENDIX 3—COPY GENERATION MANAGEMENT SYSTEM (CGMS)

- APPENDIX 4—WIDE SCREEN SIGNALING (WSS)

- APPENDIX 5—TELETEXT

- APPENDIX 6—WAVEFORMS

- APPENDIX 7—OPTIONAL OUTPUT FILTER

- APPENDIX 8—RECOMMENDED REGISTER VALUES

- OUTLINE DIMENSIONS

ADV7174/ADV7179

Rev. B | Page 30 of 52

MODE REGISTER 2 (MR2)

Bits: MR27–MR20

Address: SR4–SR0 = 02H

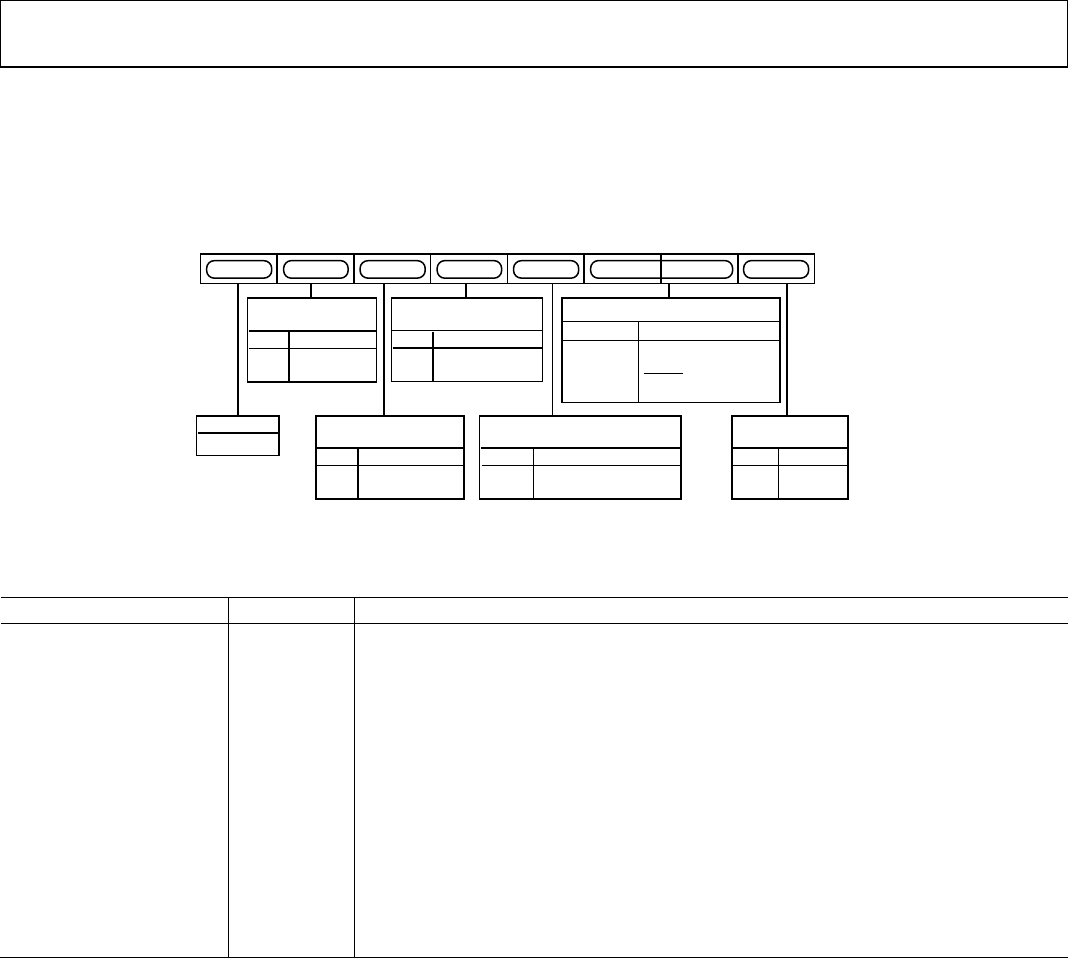

Mode Register 2 is an 8-bit-wide register. Figure 40 shows the various operations under the control of Mode Register 2. This register can

be read from as well as written to.

MR21

MR27

MR22MR23MR26 MR25 MR24

MR20

CHROMINANCE

CONTROL

0 ENABLE COLOR

1 DISABLE COLOR

MR24

GENLOCK CONTROL

x DISABLE GENLOCK

0 ENABLE SUBCARRIER

RESET PIN

1

0

1

1 ENABLE RTC PIN

MR22

MR21

LOW POWER MODE

0 DISABLE

1 ENABLE

MR26

SQUARE PIXEL

CONTROL

0 DISABLE

1 ENABLE

MR20

BURST

CONTROL

0 ENABLE BURST

1 DISABLE BURST

MR25

MR27

ACTIVE VIDEO LINE

DURATION

0 720 PIXELS

1 710 PIXELS/702 PIXELS

MR23

RESERVED

02980-A-039

Figure 40. Mode Register 2

Table 11. MR2 Bit Description

Bit Name Bit No. Description

Square Pixel Control MR20

This bit is used to set up square pixel mode. This is available in slave mode only. For NTSC, a

24.5454 MHz clock must be supplied. For PAL, a 29.5 MHz clock must be supplied.

Genlock Control MR22–MR21

These bits control the genlock feature of the ADV7174/ ADV7179. Setting MR21 to Logic 1

configures the SCRESET/RTC pin as an input. Setting MR22 to Logic 0 configures the

SCRESET/RTC pin as a subcarrier reset input. Therefore, the subcarrier will reset to Field 0

following a low-to-high transition on the SCRESET/RTC pin. Setting MR22 to Logic 1 configures

the SCRESET/RTC pin as a real-time control input.

Active Video Line Duration MR23

This bit switches between two active video line durations. A 0 selects CCIR REC601 (720 pixels

PAL/NTSC), and a 1 selects ITU-R.BT470 standard for active video duration (710 pixels NTSC

and 702 pixels PAL).

Chrominance Control MR24

This bit enables the color information to be switched on and off the video output.

Burst Control MR25

This bit enables the burst information to be switched on and off the video output.

Low Power Mode MR26

This bit enables the lower power mode of the ADV7174/ADV7179. This reduces the DAC

current by 45%.

Reserved MR27 A Logic 0 must be written to this bit.