Datasheet

Table Of Contents

- FEATURES

- APPLICATIONS

- FUNCTIONAL BLOCK DIAGRAM

- TABLE OF CONTENTS

- SPECIFICATIONS

- ABSOLUTE MAXIMUM RATINGS

- PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

- GENERAL DESCRIPTION

- TYPICAL PERFORMANCE CHARACTERISTICS

- FEATURES

- COLOR BAR GENERATION

- SQUARE PIXEL MODE

- COLOR SIGNAL CONTROL

- BURST SIGNAL CONTROL

- NTSC PEDESTAL CONTROL

- PIXEL TIMING DESCRIPTION

- SUBCARRIER RESET

- REAL-TIME CONTROL

- Video Timing Description

- Vertical Blanking Data Insertion

- Mode 0 (CCIR-656): Slave Option

- Mode 0 (CCIR-656): Master Option

- Mode 1: Slave Option HSYNC, BLANK, FIELD

- Mode 1: Master Option HSYNC, BLANK, FIELD

- Mode 2: Slave Option HSYNC, VSYNC, BLANK

- Mode 2: Master Option HSYNC, VSYNC, BLANK

- Mode 3: Master/Slave Option HSYNC, BLANK, FIELD

- POWER-ON RESET

- SCH PHASE MODE

- MPU PORT DESCRIPTION

- REGISTER ACCESSES

- REGISTER PROGRAMMING

- SUBADDRESS REGISTER (SR7–SR0)

- REGISTER SELECT (SR5–SR0)

- MODE REGISTER 1 (MR1)

- MODE REGISTER 2 (MR2)

- MODE REGISTER 3 (MR3)

- MODE REGISTER 4 (MR4)

- TIMING MODE REGISTER 0 (TR0)

- TIMING MODE REGISTER 1 (TR1)

- SUBCARRIER FREQUENCY REGISTERS 3–0

- SUBCARRIER PHASE REGISTER

- CLOSED CAPTIONING EVEN FIELD DATA REGISTERS 1–0

- CLOSED CAPTIONING ODD FIELD DATA REGISTERS 1–0

- NTSC PEDESTAL/PAL TELETEXT CONTROL REGISTERS 3–0

- TELETEXT REQUEST CONTROL REGISTER (TC07)

- CGMS_WSS REGISTER 0 (C/W0)

- CGMS_WSS REGISTER 1 (C/W1)

- CGMS_WSS REGISTER 2 (C/W2)

- APPENDIX 1—BOARD DESIGN AND LAYOUT CONSIDERATIONS

- APPENDIX 2—CLOSED CAPTIONING

- APPENDIX 3—COPY GENERATION MANAGEMENT SYSTEM (CGMS)

- APPENDIX 4—WIDE SCREEN SIGNALING (WSS)

- APPENDIX 5—TELETEXT

- APPENDIX 6—WAVEFORMS

- APPENDIX 7—OPTIONAL OUTPUT FILTER

- APPENDIX 8—RECOMMENDED REGISTER VALUES

- OUTLINE DIMENSIONS

ADV7174/ADV7179

Rev. B | Page 22 of 52

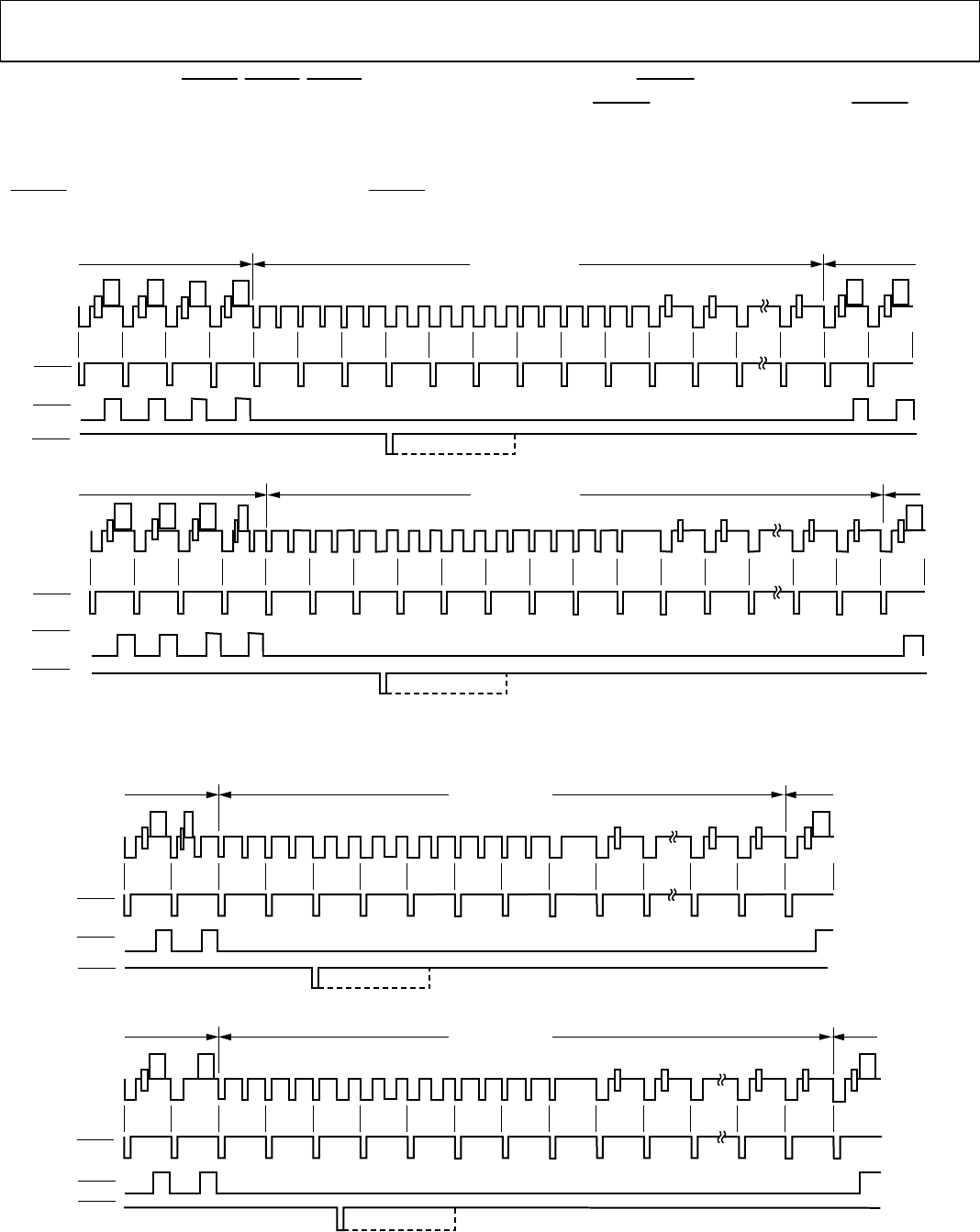

Mode 2: Slave Option

HSYNC

,

VSYNC

,

BLANK

(Timing Register 0 TR0 = X X X X X 1 0 0)

In this mode, the ADV7174/ADV7179 accepts horizontal and

vertical SYNC signals. A coincident low transition of both and

VSYNC

inputs indicates the start of an odd field. A

VSYNC

low

transition when

HSYNC

is high indicates the start of an even

field. The

BLANK

signal is optional. When the

BLANK

input is

disabled, the ADV7174/ADV7179 automatically blanks all

normally blank lines as per CCIR-624. Mode 2 is illustrated in

(NTSC) and (PAL). Figure 27 Figure 28

522

523

524

525

1

2

3

4

5

6

7

8

9

10

11

20

21

22

DISPLAY

DISPLAY

ODD FIELD

EVEN FIELD

HSYNC

BLANK

VSYNC

260

261

262

263

264

265

266

267

268

269

270

271

272

273

274

283

284

285

ODD FIELD

EVEN FIELD

DISPLAY

DISPLAY

HSYNC

BLANK

VSYNC

VERTICAL BLANK

VERTICAL BLANK

02980-A-027

Figure 27. Timing Mode 2 (NTSC)

622 623 624 625 1 2 3 4 5 6 7

21 22 23

DISPLAY

ODD FIELD

EVEN FIELD

HSYNC

BLANK

VSYNC

DISPLAY

309 310 311 312 313 314 315 316

317

318 319

334

335 336

DISPLAY

ODD FIELD EVEN FIELD

HSYNC

BLANK

DISPLAY

320

VSYNC

VERTICAL BLANK

VERTICAL BLANK

02980-A-028

Figure 28. Timing Mode 2 (PAL)