Datasheet

Table Of Contents

- FEATURES

- APPLICATIONS

- FUNCTIONAL BLOCK DIAGRAM

- TABLE OF CONTENTS

- SPECIFICATIONS

- ABSOLUTE MAXIMUM RATINGS

- PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

- GENERAL DESCRIPTION

- TYPICAL PERFORMANCE CHARACTERISTICS

- FEATURES

- COLOR BAR GENERATION

- SQUARE PIXEL MODE

- COLOR SIGNAL CONTROL

- BURST SIGNAL CONTROL

- NTSC PEDESTAL CONTROL

- PIXEL TIMING DESCRIPTION

- SUBCARRIER RESET

- REAL-TIME CONTROL

- Video Timing Description

- Vertical Blanking Data Insertion

- Mode 0 (CCIR-656): Slave Option

- Mode 0 (CCIR-656): Master Option

- Mode 1: Slave Option HSYNC, BLANK, FIELD

- Mode 1: Master Option HSYNC, BLANK, FIELD

- Mode 2: Slave Option HSYNC, VSYNC, BLANK

- Mode 2: Master Option HSYNC, VSYNC, BLANK

- Mode 3: Master/Slave Option HSYNC, BLANK, FIELD

- POWER-ON RESET

- SCH PHASE MODE

- MPU PORT DESCRIPTION

- REGISTER ACCESSES

- REGISTER PROGRAMMING

- SUBADDRESS REGISTER (SR7–SR0)

- REGISTER SELECT (SR5–SR0)

- MODE REGISTER 1 (MR1)

- MODE REGISTER 2 (MR2)

- MODE REGISTER 3 (MR3)

- MODE REGISTER 4 (MR4)

- TIMING MODE REGISTER 0 (TR0)

- TIMING MODE REGISTER 1 (TR1)

- SUBCARRIER FREQUENCY REGISTERS 3–0

- SUBCARRIER PHASE REGISTER

- CLOSED CAPTIONING EVEN FIELD DATA REGISTERS 1–0

- CLOSED CAPTIONING ODD FIELD DATA REGISTERS 1–0

- NTSC PEDESTAL/PAL TELETEXT CONTROL REGISTERS 3–0

- TELETEXT REQUEST CONTROL REGISTER (TC07)

- CGMS_WSS REGISTER 0 (C/W0)

- CGMS_WSS REGISTER 1 (C/W1)

- CGMS_WSS REGISTER 2 (C/W2)

- APPENDIX 1—BOARD DESIGN AND LAYOUT CONSIDERATIONS

- APPENDIX 2—CLOSED CAPTIONING

- APPENDIX 3—COPY GENERATION MANAGEMENT SYSTEM (CGMS)

- APPENDIX 4—WIDE SCREEN SIGNALING (WSS)

- APPENDIX 5—TELETEXT

- APPENDIX 6—WAVEFORMS

- APPENDIX 7—OPTIONAL OUTPUT FILTER

- APPENDIX 8—RECOMMENDED REGISTER VALUES

- OUTLINE DIMENSIONS

ADV7174/ADV7179

Rev. B | Page 19 of 52

622 623 624 625 1 2 3 4

5

67

21

22 23

DISPLAY

DISPLAY

VERTICAL BLANK

H

V

F

ODD FIELDEVEN FIELD

309 310 311 312 314 315 316 317

318

319 320

334

335 336

DISPLAY

DISPLAY

VERTICAL BLANK

H

V

F

ODD FIELD

EVEN FIELD

313

02980-A-022

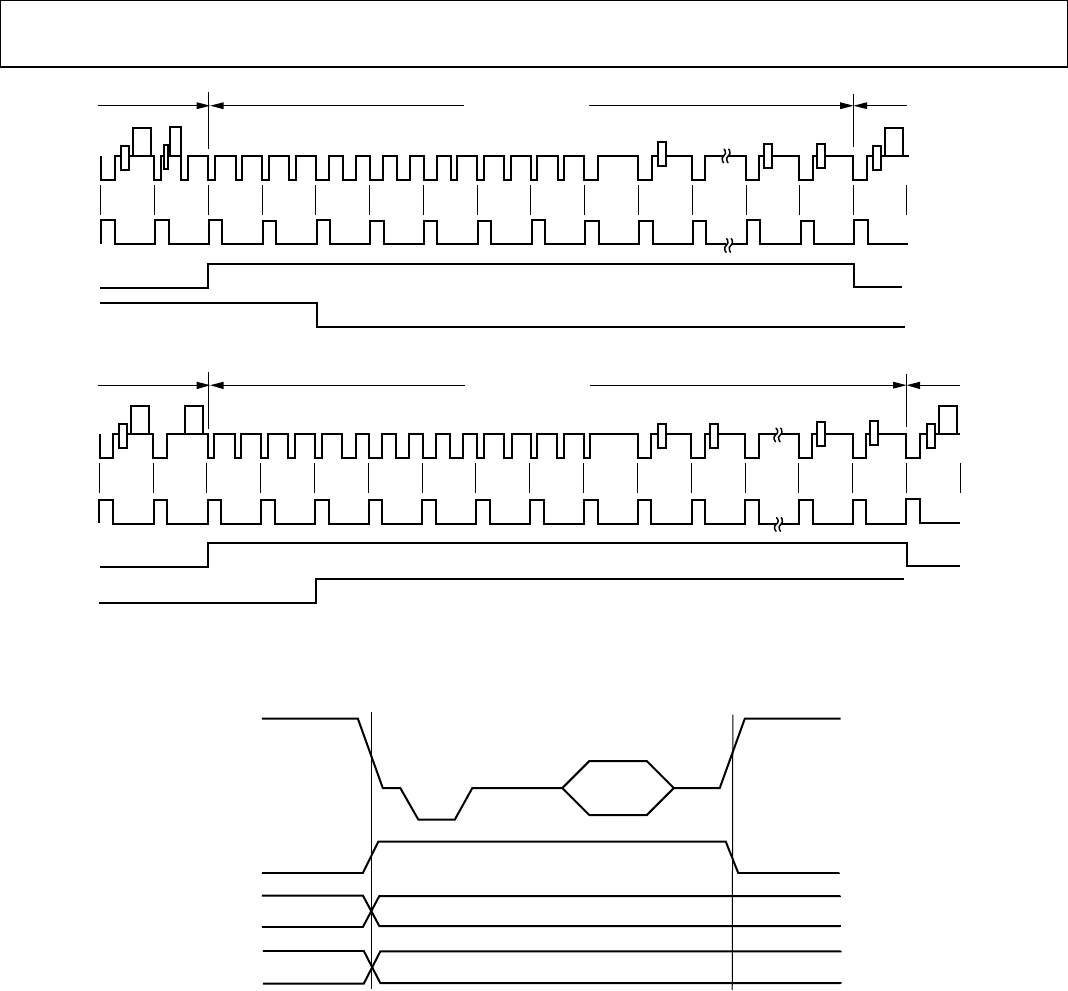

Figure 22. Timing Mode 0 (PAL Master Mode)

A

NALO

G

VIDEO

H

F

V

02980-A-023

Figure 23. Timing Mode 0 Data Transitions (Master Mode)