Datasheet

Table Of Contents

- FEATURES

- APPLICATIONS

- FUNCTIONAL BLOCK DIAGRAM

- TABLE OF CONTENTS

- SPECIFICATIONS

- ABSOLUTE MAXIMUM RATINGS

- PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

- GENERAL DESCRIPTION

- TYPICAL PERFORMANCE CHARACTERISTICS

- FEATURES

- COLOR BAR GENERATION

- SQUARE PIXEL MODE

- COLOR SIGNAL CONTROL

- BURST SIGNAL CONTROL

- NTSC PEDESTAL CONTROL

- PIXEL TIMING DESCRIPTION

- SUBCARRIER RESET

- REAL-TIME CONTROL

- Video Timing Description

- Vertical Blanking Data Insertion

- Mode 0 (CCIR-656): Slave Option

- Mode 0 (CCIR-656): Master Option

- Mode 1: Slave Option HSYNC, BLANK, FIELD

- Mode 1: Master Option HSYNC, BLANK, FIELD

- Mode 2: Slave Option HSYNC, VSYNC, BLANK

- Mode 2: Master Option HSYNC, VSYNC, BLANK

- Mode 3: Master/Slave Option HSYNC, BLANK, FIELD

- POWER-ON RESET

- SCH PHASE MODE

- MPU PORT DESCRIPTION

- REGISTER ACCESSES

- REGISTER PROGRAMMING

- SUBADDRESS REGISTER (SR7–SR0)

- REGISTER SELECT (SR5–SR0)

- MODE REGISTER 1 (MR1)

- MODE REGISTER 2 (MR2)

- MODE REGISTER 3 (MR3)

- MODE REGISTER 4 (MR4)

- TIMING MODE REGISTER 0 (TR0)

- TIMING MODE REGISTER 1 (TR1)

- SUBCARRIER FREQUENCY REGISTERS 3–0

- SUBCARRIER PHASE REGISTER

- CLOSED CAPTIONING EVEN FIELD DATA REGISTERS 1–0

- CLOSED CAPTIONING ODD FIELD DATA REGISTERS 1–0

- NTSC PEDESTAL/PAL TELETEXT CONTROL REGISTERS 3–0

- TELETEXT REQUEST CONTROL REGISTER (TC07)

- CGMS_WSS REGISTER 0 (C/W0)

- CGMS_WSS REGISTER 1 (C/W1)

- CGMS_WSS REGISTER 2 (C/W2)

- APPENDIX 1—BOARD DESIGN AND LAYOUT CONSIDERATIONS

- APPENDIX 2—CLOSED CAPTIONING

- APPENDIX 3—COPY GENERATION MANAGEMENT SYSTEM (CGMS)

- APPENDIX 4—WIDE SCREEN SIGNALING (WSS)

- APPENDIX 5—TELETEXT

- APPENDIX 6—WAVEFORMS

- APPENDIX 7—OPTIONAL OUTPUT FILTER

- APPENDIX 8—RECOMMENDED REGISTER VALUES

- OUTLINE DIMENSIONS

ADV7174/ADV7179

Rev. B | Page 10 of 52

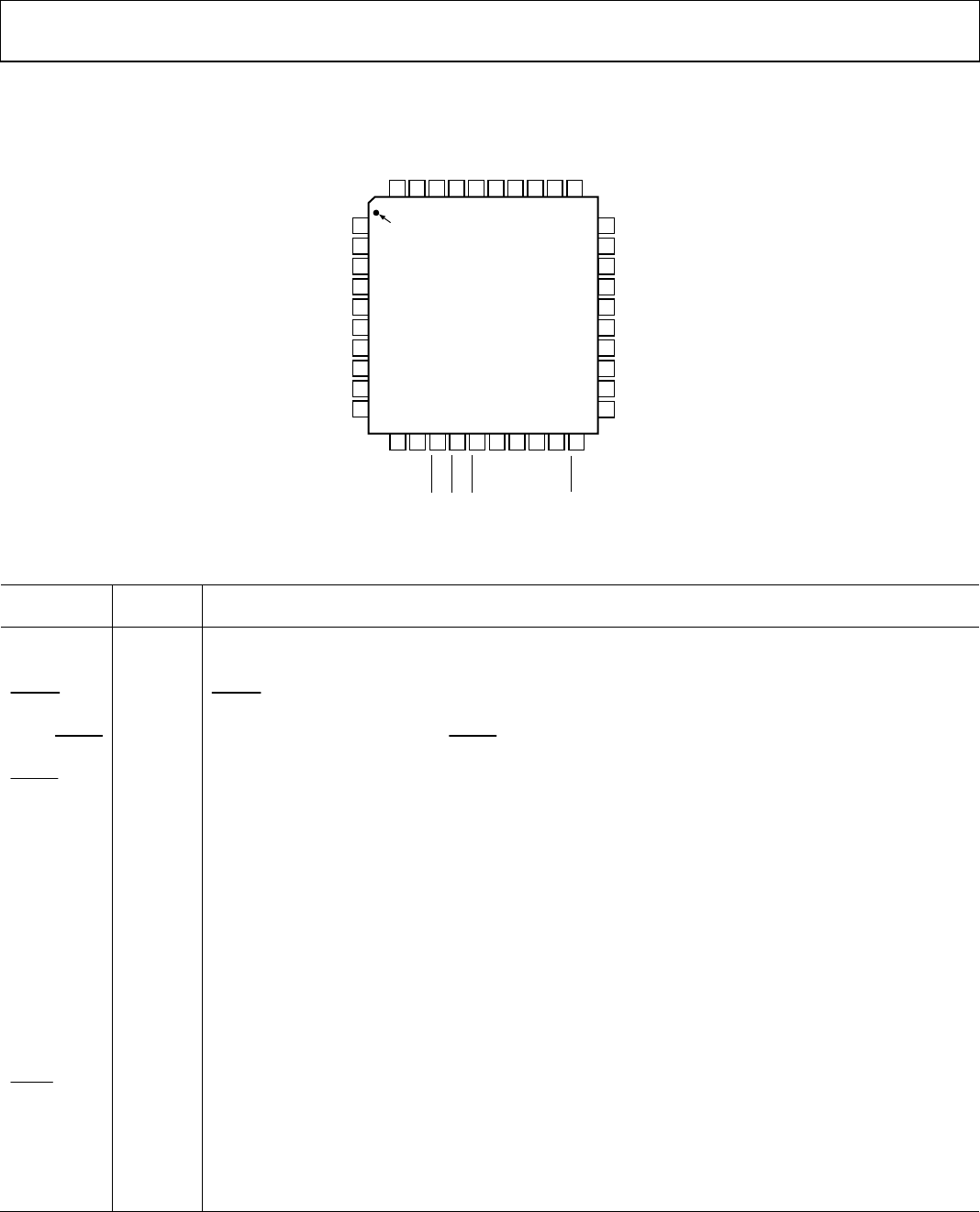

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

37 36 3538

39

40 33 32 3134

11

12 13 14 15 16 17

18

19 20

3

4

5

6

7

1

2

10

8

9

26

27

28

29

24

25

22

23

21

30

V

REF

DAC A

DAC B

V

AA

GND

V

AA

DAC C

BLANK

GND

GND

HSYNC

FIELD/VSYNC

ALSB

C

LOC

K

V

AA

P5

P6

P7

GND

GND

GND

GND

V

AA

COMP

SDATA

SCLOCK

GND

V

AA

GND

RESET

GND

P4

P3

P2

P1

P0

TTX

TTXREQ

R

SET

SCRESET/

RTC

PIN 1

INDICATOR

ADV7174/ADV7179

LFCSP

TOP VIEW

(Not to Scale)

02980-A-005

Figure 5. Pin Configurations

Table 6. Pin Function Descriptions

Mnemonic

Input/

Output Function

P7–P0 I 8-Bit 4:2:2 Multiplexed YCrCb Pixel Port (P7–P0). P0 is the LSB.

CLOCK I

TTL Clock Input. Requires a stable 27 MHz reference clock for standard operation. Alternatively, a 24.5454 MHz

(NTSC) or 29.5 MHz (PAL) can be used for square pixel operation.

HSYNC

I/O

HSYNC

(Modes 1 and 2) Control Signal. This pin may be configured to output (master mode) or accept (slave

mode) sync signals.

FIELD/VSYNC

I/O

Dual Function FIELD (Mode 1) and VSYNC (Mode 2) Control Signal. This pin may be configured to output

(master mode) or accept (slave mode) these control signals.

BLANK

I/O Video Blanking Control Signal. The pixel inputs are ignored when this is Logic 0. This signal is optional.

SCRESET/RTC I

This pin can be configured as an input by setting MR22 and MR21 of Mode Register 2. It can be configured as a

subcarrier reset pin, in which case a low-to-high transition on this pin resets the subcarrier to Field 0.

Alternatively, it can be configured as a real-time control (RTC) input.

V

REF

I/O Voltage Reference Input for DACs or Voltage Reference Output (1.235 V).

R

SET

I A 150 Ω resistor connected from this pin to GND is used to control full-scale amplitudes of the video signals.

COMP O

Compensation Pin. Connect a 0.1 μF capacitor from COMP to V

AA

. For optimum dynamic performance in low

power mode, the value of the COMP capacitor can be lowered to as low as 2.2 nF.

DAC A O DAC Output (see Table 13)

DAC B O DAC Output (see Table 13).

DAC C O DAC Output (see Table 13).

SCLOCK I MPU Port Serial Interface Clock Input.

SDATA I/O MPU Port Serial Data Input/Output.

ALSB I TTL Address Input. This signal sets up the LSB of the MPU address.

RESET

I

This input resets the on-chip timing generator and sets the ADV7174/ADV7179 into default mode. This is NTSC

operation, Timing Slave Mode 0, 8-bit operation, 2× composite out signals. DACs A, B, and C are enabled.

TTX I Teletext Data.

TTXREQ O Teletext Data Request Signal/Defaults to GND when Teletext Not Selected.

V

AA

P Power Supply (2.8 V or 3.3 V).

GND G Ground Pin.